### Side-Channel Security of Embedded Devices

by

Ing. Petr Socha

A dissertation thesis submitted to

the Faculty of Information Technology, Czech Technical University in Prague, in partial fulfilment of the requirements for the degree of Doctor.

Doctoral study programme: Informatics Department of Digital Design

Prague, May 2023

#### Supervisor:

Dr.-Ing. Martin Novotný Department of Digital Design Faculty of Information Technology Czech Technical University in Prague Thákurova 9 160 00 Prague 6 Czech Republic

#### **Co-Supervisor:**

Ing. Vojtěch Miškovský, Ph.D. Department of Digital Design Faculty of Information Technology Czech Technical University in Prague Thákurova 9 160 00 Prague 6 Czech Republic

Copyright © 2023 Ing. Petr Socha

### Abstract and contributions

This dissertation thesis focuses on the physical security of cryptographic implementations in embedded devices, especially resistance to side-channel attacks such as differential power analysis. Attention is paid to both symmetric encryption algorithms (PRESENT, AES, Serpent) and the post-quantum asymmetric Rainbow signature scheme. Security of symmetric cryptography is mainly investigated on a Field Programmable Gate Arrays (FPGA) hardware platform, where countermeasures are proposed for design and synthesis on register-transfer and system levels. Asymmetric cryptography is mainly investigated on software platforms, where an attack on the reference Rainbow implementation is discussed and a multi-platform countermeasure against such attacks is proposed. All of the proposed countermeasures are evaluated in terms of time and space requirements and their effectiveness is evaluated using leakage assessment methodology.

The main contributions of the dissertation thesis are based on peer-reviewed and published papers, here presented as follows:

- 1. Survey of the current state of the art in the field of side-channel analysis.

- 2. Design, implementation, and evaluation of countermeasures, based on a dynamic reconfiguration of combinational logic, for AES and Serpent on FPGA, and designed for register transfer level synthesis.

- 3. Design, implementation, and evaluation of countermeasures for PRESENT, AES, and Serpent on FPGA, described at system level and designed for high-level synthesis.

- 4. Design, implementation, and evaluation of an attack on the 32-bit reference implementation of Rainbow on an ARM-based microcontroller.

- 5. Proposal of a countermeasure for multivariate quadratic signature schemes based on the principle of equivalent keys, its formal examination, implementation for Rainbow, and evaluation on an ARM-based microcontroller.

#### Keywords:

Embedded Systems, Cryptography, Side-Channel Security, Internet of Things.

## Abstrakt a přínosy (Czech)

Tato dizertační práce se zabývá fyzickou bezpečností kryptografických implementací ve vestavných zařízeních, konkrétně odolností proti útokům postranními kanály, mezi něž patří například rozdílová odběrová analýza. Pozornost je věnována jak symetrickým šifrovacím algoritmům (PRESENT, AES, Serpent), tak asymetrickému podpisovému schéma Rainbow. Bezpečnost symetrické kryptografie je zkoumána především na hardwarové platformě založené na programovatelném hradlovém poli (FPGA), kde jsou navržena protiopatření jak pro návrh na úrovni meziregistrových přenosů, tak na systémové úrovni. Asymetrická kryptografie je zkoumána především na softwarové platformě, kde je navržen útok na referenční implementaci Rainbow a následně je navrženo multiplatformní protiopatření proti takovým útokům. Všechna navržená protiopatření jsou vyhodnocena z hlediska časové a prostorové náročnosti a jejich účinnost je ověřena pomocí vhodné metodologie.

Hlavní přínosy této dizertační práce vycházejí z recenzovaných a publikovaných článků, zde prezentovaných následovně:

- 1. Shrnutí současného stavu poznání v oboru analýzy postranních kanálů.

- 2. Návrh, implementace a vyhodnocení protiopatření, založených na dynamické rekonfiguraci kombinační logiky, pro AES a Serpent na FPGA, určených pro syntézu na úrovni meziregistrových přenosů.

- 3. Návrh, implementace a vyhodnocení protiopatření pro PRESENT, AES a Serpent na FPGA, popsaných na systémové úrovni a určených pro vysokoúrovňovou syntézu.

- 4. Návrh, implementace a vyhodnocení útoku na 32<br/>bitovou referenční implementaci Rainbow na mikrokontroléru s jádrem ARM.

- 5. Návrh protiopatření pro multivarietní kvadratická podpisová schémata založeného na principu ekvivalentních klíčů, jeho formální analýza a implementace pro Rainbow a vyhodnocení na mikrokontroléru s jádrem ARM.

#### Klíčová slova:

Vestavné systémy, kryptografie, bezpečnost postranních kanálů, internet věcí.

## Acknowledgement

First of all, I would like to thank my supervisor Martin Novotný for his help during my studies, his valuable insights, for involving me in many different projects, and for introducing me to many interesting people. I would also like to thank my co-supervisor Vojtěch Miškovský for his insights and cooperation, and for convincing me to do my research in the first place. I would also like to thank my student and colleague David Pokorný for a productive collaboration. Many thanks to my colleague Jan Onderka for helpful discussions, proofreading of my work, and for providing a sober perspective. Many thanks also to Hana Kubátová and the entire Department of Digital Design for providing a friendly and helpful environment for my research.

A big thank you goes to my grandfather Josef, who taught me to build my own electrical circuits and program my first 386 PC when I was just a little boy, thus predetermining my whole life. Special thanks to my music teacher Karel Bareš, who taught me calmness, perseverance, and prudence. I must not forget my friends, Martin, Honza, Zdeněk, Petr, Milan, Filip, Marek, and others, who had a great influence on me at one time or another in my life, and who gave me the strength to carry on. Finally, my biggest thanks go to my parents Jana and Petr for their unwavering support in everything I do.

The research presented in this thesis has been partially supported by the following grants:

- "Fault-Tolerant and Attack-Resistant Architectures Based on Programmable Devices: Research of Interplay and Common Features" (GA16-05179S) of The Czech Science Foundation (2016-2018).

- "DRASTIC: Dynamically Reconfigurable Architectures for Side-channel analysis protecTIon of Cryptographic implementations" of the Central Europe Leuven Strategic Alliance (CELSA) (2017-2019).

- "Tools for AI-enhanced Security Verification of Cryptographic Devices" (VJ02010010) of the Ministry of the Interior of the Czech Republic (2022-2025).

"Dependable and attack-resistant architectures for programmable devices" (2017-2019, SGS17/213/OHK3/3T/18), "Design, programming and verification of embedded systems" (2020-2022, SGS20/211/OHK3/3T/18), "Design, programming and verification of intelligent embedded systems" (2023-2025, SGS23/208/OHK3/3T/18) of the Student Grant Competition of CTU in Prague.

Dedication

To all my loves, past, present, and to come.

## Contents

| 1        | Intr | troduction                                     |      |      |    |     |    |   |   |   |   |   |   |   | 1  |

|----------|------|------------------------------------------------|------|------|----|-----|----|---|---|---|---|---|---|---|----|

|          | 1.1  | Motivation and Problem Statement               |      |      |    |     |    |   |   |   |   |   |   |   | 1  |

|          | 1.2  | 2 Goals of the Dissertation Thesis             |      |      |    |     |    |   |   |   |   |   |   |   | 2  |

|          | 1.3  | 3 Structure of the Dissertation Thesis         |      | •    |    | •   | •  | • | • | • | • | • | • | • | 2  |

| <b>2</b> | Bac  | ackground and State of the Art                 |      |      |    |     |    |   |   |   |   |   |   |   | 3  |

|          | 2.1  | Introduction to Side-Channel Security          |      |      |    |     |    |   |   |   |   |   |   |   | 3  |

|          |      | 2.1.1 Measurements                             |      |      |    |     |    |   |   |   |   |   |   |   | 6  |

|          |      | 2.1.2 Formal Model                             |      |      |    |     |    |   |   |   |   |   |   |   | 8  |

|          |      | 2.1.3 Leakage Function                         |      |      |    |     |    |   |   |   |   |   |   |   | 10 |

|          | 2.2  | -                                              |      |      |    |     |    |   |   |   |   |   |   |   | 11 |

|          |      | 2.2.1 Differential Power Analysis (DPA)        |      |      |    |     |    |   |   |   |   |   |   |   | 12 |

|          |      | 2.2.2 Multi-bit DPA and Partitioning Power An  | naly | vsis | (1 | PP. | A) |   |   |   |   |   |   |   | 13 |

|          |      | 2.2.3 Correlation Power Analysis (CPA)         |      |      |    |     |    |   |   |   |   |   |   |   | 14 |

|          |      | 2.2.4 Mutual Information Analysis (MIA)        |      |      |    |     |    |   |   |   |   |   |   |   | 16 |

|          |      | 2.2.5 Kolmogorov–Smirnov Analysis (KSA)        |      |      |    |     |    |   |   |   |   |   |   |   | 18 |

|          |      | 2.2.6 Differential Deep Learning Analysis (DDI |      |      |    |     |    |   |   |   |   |   |   |   | 19 |

|          | 2.3  | B Profiled Attacks                             |      |      |    |     |    |   |   |   |   |   |   |   | 20 |

|          |      | 2.3.1 Template Attack (TA)                     |      |      |    |     |    |   |   |   |   |   |   |   | 20 |

|          |      | 2.3.2 Machine Learning-based Attacks           |      |      |    |     |    |   |   |   |   |   |   |   | 24 |

|          | 2.4  | Side-Channel Attack Related Metrics            |      |      |    |     |    |   |   |   |   |   |   |   | 25 |

|          |      | 2.4.1 Success Rate and Guessing Entropy        |      |      |    |     |    |   |   |   |   |   |   |   | 25 |

|          |      | 2.4.2 Confusion Coefficient and Distinguishing |      |      |    |     |    |   |   |   |   |   |   |   | 26 |

|          | 2.5  |                                                |      |      |    |     |    |   |   |   |   |   |   |   | 27 |

|          |      | 2.5.1 Secure Logic Styles                      |      |      |    |     |    |   |   |   |   |   |   |   | 28 |

|          |      | 2.5.2 Additional Modules                       |      |      |    |     |    |   |   |   |   |   |   |   | 28 |

|          |      | 2.5.3 Masking                                  |      |      |    |     |    |   |   |   |   |   |   |   | 29 |

|          | 2.6  | -                                              |      |      |    |     |    |   |   |   |   |   |   |   | 32 |

|   | 2.7 | 2.6.1<br>2.6.2<br>Leakag<br>2.7.1<br>2.7.2<br>2.7.3 | Attacks on Masking       3         ge Assessment       3         Welch's t-test       3         Chi-squared test       3 | 2<br>3<br>5<br>6<br>7 |

|---|-----|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------|

|   |     | 2.1.3                                               | Deep Learning Leakage Assessment                                                                                         | 1                     |

| 3 | v   |                                                     | c Cryptography 3                                                                                                         |                       |

|   | 3.1 |                                                     | tution-Permutation Networks                                                                                              |                       |

|   |     | 3.1.1                                               |                                                                                                                          | 0                     |

|   |     | 3.1.2                                               | 7 3                                                                                                                      | 0                     |

|   |     | 3.1.3                                               | 1                                                                                                                        | 1                     |

|   | 3.2 | Combi                                               |                                                                                                                          | 1                     |

|   |     | 3.2.1                                               | Dynamic Logic Reconfiguration using CFGLUTs 4                                                                            |                       |

|   |     | 3.2.2                                               |                                                                                                                          | 2                     |

|   |     | 3.2.3                                               | Proposed Secure Cipher Design                                                                                            | 5                     |

|   |     | 3.2.4                                               | Latency and Area Utilization                                                                                             | 7                     |

|   |     | 3.2.5                                               | Side-Channel Leakage Evaluation                                                                                          | 7                     |

|   |     | 3.2.6                                               | Further Experiments                                                                                                      | 3                     |

|   |     | 3.2.7                                               | Summary                                                                                                                  | 4                     |

|   | 3.3 | High-I                                              | Level Synthesis of Masking Countermeasure                                                                                | 5                     |

|   |     | 3.3.1                                               | FPGA Design using High-Level Synthesis                                                                                   | 6                     |

|   |     | 3.3.2                                               | Alternating Masks Scheme                                                                                                 | 7                     |

|   |     | 3.3.3                                               | Proposed Secure Cipher Design                                                                                            | 7                     |

|   |     | 3.3.4                                               | Latency, Throughput and Area Utilization                                                                                 | 0                     |

|   |     | 3.3.5                                               | Side-Channel Leakage Evaluation                                                                                          | 2                     |

|   |     | 3.3.6                                               | Discussion and Future Work                                                                                               | 9                     |

|   |     | 3.3.7                                               | Summary                                                                                                                  | 0                     |

|   | 3.4 | Summ                                                | ary                                                                                                                      | '1                    |

| 4 | Asv | mmeti                                               | ric Cryptography 7                                                                                                       | 3                     |

| - | 4.1 |                                                     |                                                                                                                          | '4                    |

|   |     | 4.1.1                                               | • 0                                                                                                                      | 5                     |

|   |     | 4.1.2                                               |                                                                                                                          | '6                    |

|   |     | 4.1.3                                               | 1 1                                                                                                                      | 7                     |

|   |     | 4.1.4                                               |                                                                                                                          | 7                     |

|   | 4.2 |                                                     | 0 0                                                                                                                      | 7                     |

|   | 1.4 | 4.2.1                                               | -                                                                                                                        | '8                    |

|   |     | 4.2.2                                               | 1                                                                                                                        | 0<br>50               |

|   |     | 4.2.3                                               | 1                                                                                                                        | 51                    |

|   |     | 4.2.4                                               | 1                                                                                                                        | 51                    |

|   |     | 4.2.5                                               |                                                                                                                          | 32                    |

|   |     |                                                     |                                                                                                                          |                       |

|                                                              | 4.3   | B Equivalent Keys as a Side-Channel Countermeasure for Multivariate Quadratic |                                    |     |  |

|--------------------------------------------------------------|-------|-------------------------------------------------------------------------------|------------------------------------|-----|--|

|                                                              |       | Signat                                                                        | ures                               | 82  |  |

|                                                              |       | 4.3.1                                                                         | Equivalent Key                     | 83  |  |

|                                                              |       | 4.3.2                                                                         | Efficient Implementation           | 89  |  |

|                                                              |       | 4.3.3                                                                         | Side-Channel Leakage Evaluation    | 95  |  |

|                                                              |       | 4.3.4                                                                         | Time Evaluation                    | 97  |  |

|                                                              |       | 4.3.5                                                                         | Memory Evaluation                  | 100 |  |

|                                                              |       | 4.3.6                                                                         | Summary                            | 100 |  |

|                                                              | 4.4   | Summ                                                                          | ary                                | 101 |  |

| -                                                            | C     | ı •                                                                           |                                    | 100 |  |

| <b>5</b>                                                     | Con   | clusio                                                                        |                                    | 103 |  |

|                                                              | 5.1   | Summ                                                                          | ary of Contributions               | 104 |  |

|                                                              | 5.2   | Future                                                                        | e Work                             | 105 |  |

| Bi                                                           | bliog | raphy                                                                         |                                    | 107 |  |

| Reviewed Publications of the Author Presented in This Thesis |       |                                                                               |                                    |     |  |

| Re                                                           | emair | ning R                                                                        | eviewed Publications of the Author | 127 |  |

## **List of Figures**

| 2.1  | A CMOS inverter model                                                             | 5  |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | A CMOS inverter current consumption                                               | 5  |

| 2.3  | Rijndael/AES Encryption FPGA Power Trace                                          | 6  |

| 2.4  | Example of a power measurement setup                                              | 7  |

| 2.5  | Combinatorial logic delay monitors                                                | 8  |

| 2.6  | Illustration of channels involved in side-channel analysis.                       | 9  |

| 2.7  | Architecture of Rijndael/AES last round                                           | 15 |

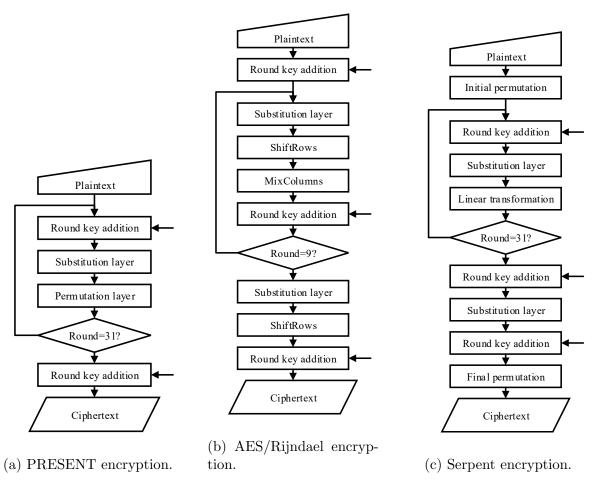

| 3.1  | Discussed symmetric encryption algorithms (128-bit key variants)                  | 40 |

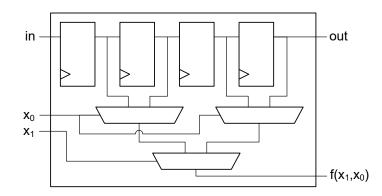

| 3.2  | Example of a 2-input reconfigurable look-up table with serial programming $I/O$ . | 42 |

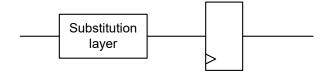

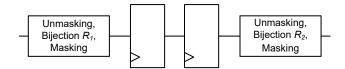

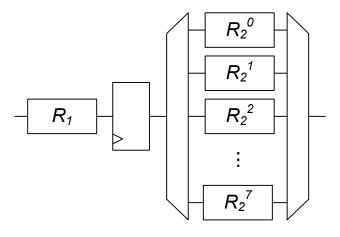

| 3.3  | S-box Decomposition.                                                              | 43 |

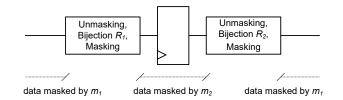

| 3.4  | S-box Decomposition + Masking                                                     | 44 |

| 3.5  | S-box Decomposition + Masking + Register Precharge                                | 45 |

| 3.6  | Serpent S-boxes decomposition.                                                    | 46 |

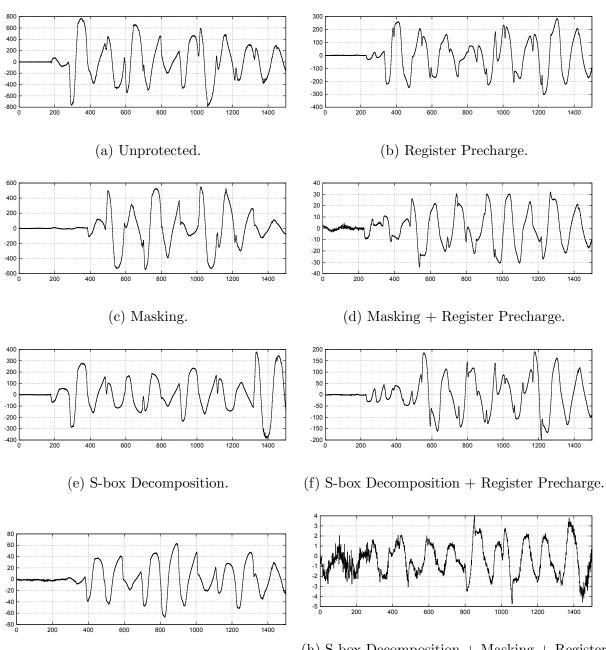

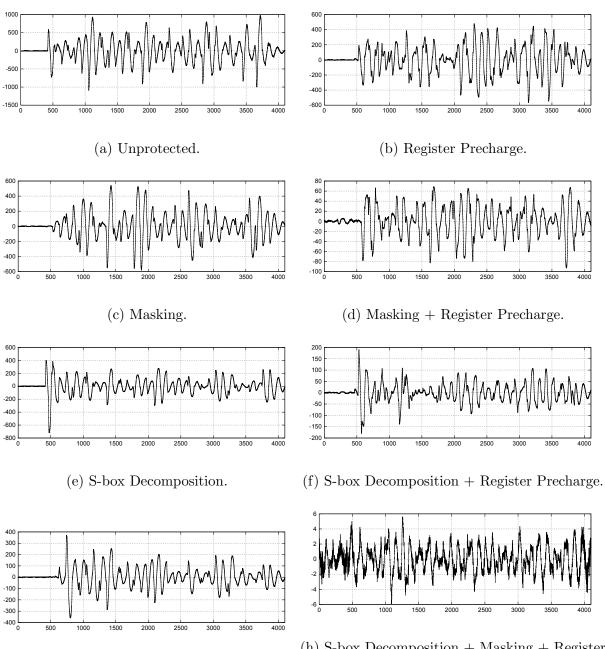

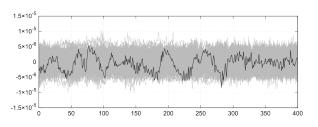

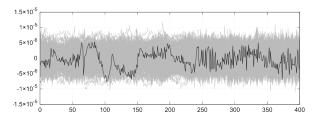

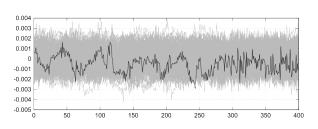

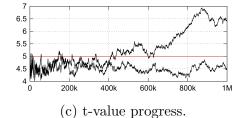

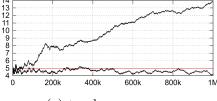

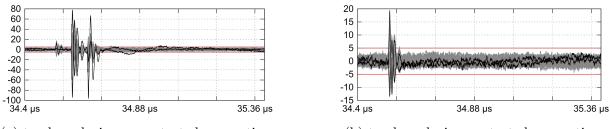

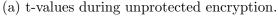

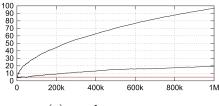

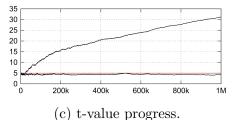

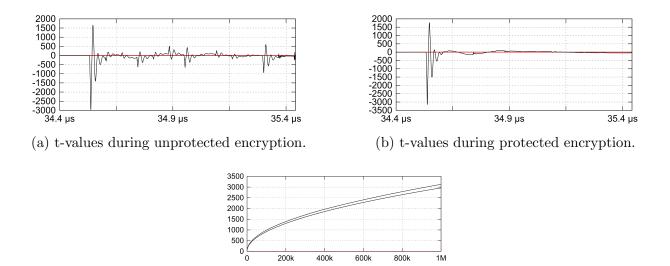

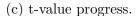

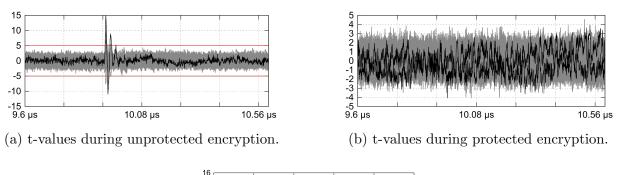

| 3.7  | Results of the AES/Rijndael t-test                                                | 49 |

| 3.8  | Results of the Serpent t-test                                                     | 50 |

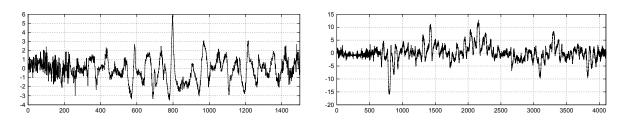

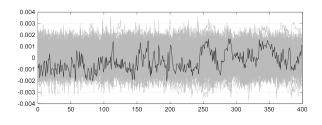

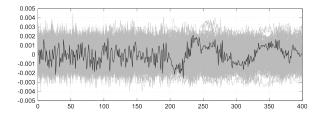

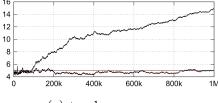

| 3.9  | Results of the univariate second-order t-test                                     | 52 |

| 3.10 | Second-order DPA attack.                                                          | 53 |

| 3.11 | Second-order CPA attack.                                                          | 54 |

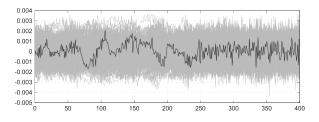

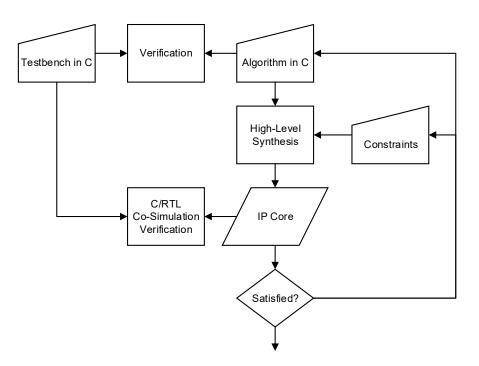

| 3.12 | Example of a design flow using high-level synthesis.                              | 56 |

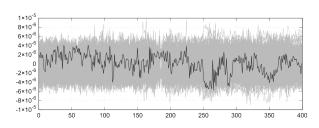

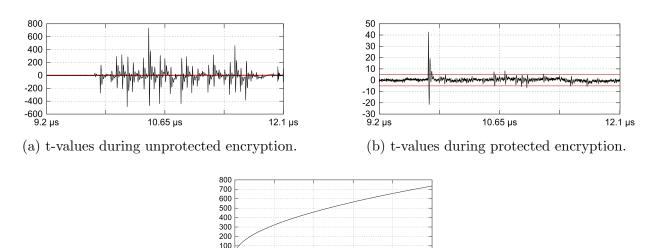

| 3.13 | PRESENT specific t-test results of 64 models based on substitution layer out-     |    |

|      | put (S-boxes outputs).                                                            | 64 |

| 3.14 | PRESENT specific t-test results of 64 models based on round register leakage      |    |

|      | (xor of consecutive rounds inputs).                                               | 65 |

| 3.15 | PRESENT non-specific t-test results                                               | 65 |

| 3.16 | AES/Rijndael specific t-test results of 128 models based on substitution layer    |    |

|      | output (S-boxes outputs).                                                         | 66 |

| 3.17 | AES/Rijndael specific t-test results of 128 models based on round register        |    |

|      | leakage (xor of consecutive rounds inputs).                                       | 66 |

| 3.18 | AES/Rijndael non-specific t-test results.                                        | 67 |

|------|----------------------------------------------------------------------------------|----|

| 3.19 | Serpent specific t-test results of 128 models based on substitution layer output |    |

|      | (S-boxes outputs).                                                               | 67 |

| 3.20 | Serpent specific t-test results of 128 models based on round register leakage    |    |

|      | (xor of consecutive rounds inputs)                                               | 68 |

| 3.21 | Serpent non-specific t-test results                                              | 68 |

| 3.22 | Results of the specific t-tests based on substitution layer output (S-boxes out- |    |

|      | puts), Version 2                                                                 | 69 |

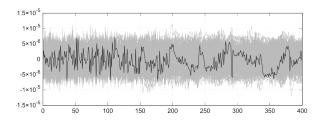

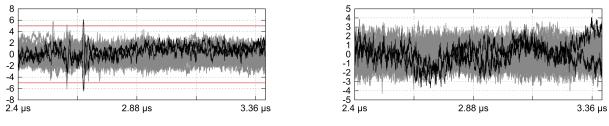

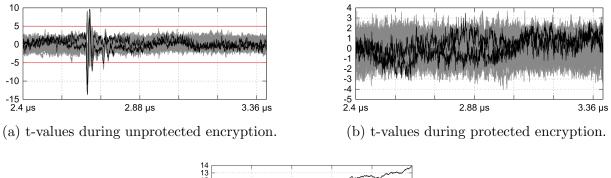

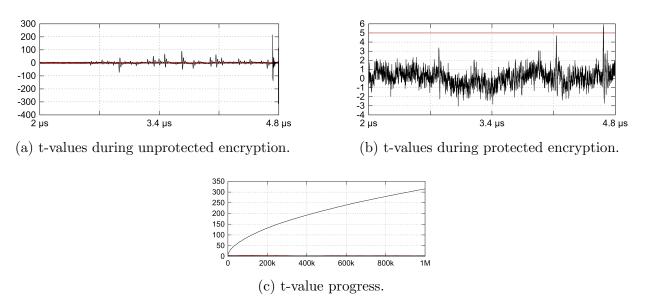

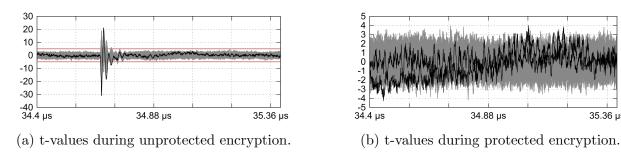

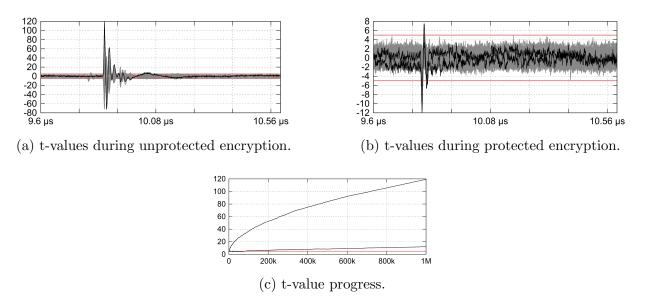

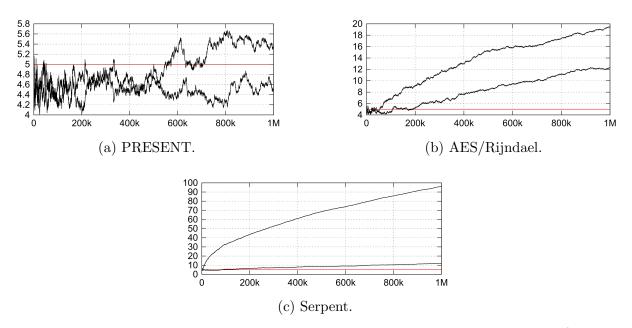

| 4.1  | Results of the t-tests (Rainbow).                                                | 97 |

|      | Execution times of the components in equivalent key generation                   | 99 |

## List of Tables

| 3.1 | Latency and Area Utilization.                           | 47 |

|-----|---------------------------------------------------------|----|

| 3.2 | Total S-box count.                                      | 58 |

| 3.3 | Post-RTL-synthesis area and timing estimates comparison | 60 |

| 4.1 | Attack I: Revealing a matrix row                        | 78 |

| 4.2 | Attack II: Row identification.                          | 79 |

| 4.3 | Attack III: Revealing remaining rows.                   | 80 |

| 4.4 | Summary of equivalent key variants.                     | 92 |

| 4.5 | Time overhead comparison.                               | 98 |

## **Abbreviations**

### Related to Cryptography and Side-Channel Analysis

| AES                    | Advanced Encryption Standard            |

|------------------------|-----------------------------------------|

| $\mathbf{CPA}$         | Correlation Power Analysis              |

| DDLA                   | Differential Deep Learning Analysis     |

| DLLA                   | Deep Learning Leakage Assessment        |

| $\mathbf{D}\mathbf{M}$ | Distinguishing Margin                   |

| DPA                    | Differential Power Analysis             |

| $\mathbf{GE}$          | Guessing Entropy                        |

| HD                     | Hamming Distance                        |

| $\mathbf{H}\mathbf{W}$ | Hamming Weight                          |

| ID                     | Identity                                |

| iKSA                   | Inter-class Kolmogorov-Smirnov Analysis |

| KSA                    | Kolmogorov-Smirnov Analysis             |

| MIA                    | Mutual Information Analysis             |

| PPA                    | Partitioning Power Analysis             |

| $\mathbf{RSA}$         | Rivest–Shamir–Adleman cryptosystem      |

| $\mathbf{SR}$          | Success Rate                            |

| TA                     | Template Attack                         |

#### Related to Digital Design and Electronics

| $\mathbf{AC}$   | Alternating Current                                                                  |

|-----------------|--------------------------------------------------------------------------------------|

| ADC             | Analog-to-Digital Converter                                                          |

| ASIC            | Application-Specific Integrated Circuit                                              |

| $\mathbf{CLK}$  | Clock                                                                                |

| CMOS            | Complementary Metal–Oxide–Semiconductor                                              |

| $\mathbf{DC}$   | Direct Current                                                                       |

| $\mathbf{EM}$   | Electromagnetic                                                                      |

| FPGA            | Field-Programmable Gate Array                                                        |

| GND             | Ground                                                                               |

| $\mathbf{HLS}$  | High-Level Synthesis                                                                 |

| MOSFET          | Metal–Oxide–Semiconductor Field-Effect Transistor                                    |

| NMOS            | N-channel Metal–Oxide–Semiconductor                                                  |

| $\mathbf{PMOS}$ | P-channel Metal–Oxide–Semiconductor                                                  |

| $\mathbf{RAM}$  | Random Access Memory                                                                 |

| $\mathbf{RTL}$  | Register-Transfer Level                                                              |

| $\mathbf{SABL}$ | Sense Amplifier-Based Logic                                                          |

| $\mathbf{SDDL}$ | Simple Dynamic Differential Logic                                                    |

| $\mathbf{SNR}$  | Signal-to-Noise Ratio                                                                |

| VHDL            | VHSIC (Very High-Speed Integrated Circuits Program)<br>Hardware Description Language |

| WDDL            | Wave Dynamic Differential Logic                                                      |

| XOR             | Exclusive OR                                                                         |

#### Miscellaneous

| $\mathbf{CNN}$       | Convolutional Neural Network                   |

|----------------------|------------------------------------------------|

| $\mathbf{CPU}$       | Central Processing Unit                        |

| $\mathbf{DL}$        | Deep Learning                                  |

| $\mathbf{GPU}$       | Graphics Processing Unit                       |

| IoT                  | Internet of Things                             |

| $\mathbf{ML}$        | Machine Learning                               |

| $\operatorname{MLP}$ | Multilayer Perceptron                          |

| NIST                 | National Institute of Standards and Technology |

| OpenCL               | Open Computing Language                        |

| OpenMP               | Open Multi-Processing                          |

| $\mathbf{SVM}$       | Support Vector Machine                         |

Mathematical notation and the used formal model is presented in subsection 2.1.2.

CHAPTER

## Introduction

### 1.1 Motivation and Problem Statement

In the past few decades, computer systems and communication networks have become an essential part of our everyday lives. Various computing devices are used not only as tools for many professionals, but also for entertainment. These devices include embedded devices, such as payment cards, biometric passports, smart cars, trains or whole cities, and even medical devices like pacemakers. Being surrounded by devices connected to the Internet, our private lives are endangered more than ever [156].

Special attention must be given to ensure security of computer systems and their users. Various measures are employed to achieve confidentiality, integrity, availability, and non-repudiation of data with efficiency, ease of use, and cost in mind. Nowadays, widely used algorithms such as AES [45, 120] or RSA [144] are typically considered secure from the cryptanalytic point of view. However, their implementations may leak sensitive information through side channels of the used cryptographic device, potentially compromising the entire system.

Side-channel attacks exploit the data-dependent side channels, such as power consumption of the cryptographic device [84, 83] or its electromagnetic radiation [136], in order to extract secret information such as cipher keys. Such attacks pose a severe threat to both hardware and software cryptographic implementations, especially in the IoT environment where the attacker may easily gain physical access to the device, leaving it vulnerable to tampering. Various countermeasures have been proposed to prevent such attacks. Masking is a widely used technique based on randomization of the processed data [39, 109, 122, 63], making it difficult to exploit the leakage. Another common approach is hiding, which aims to conceal the exploitable leakage in either side-channel signal amplitude or time [167, 168, 64, 108]. Recent real-world attack examples show that uncompromising protection and testing of embedded cryptographic implementations is necessary [95].

## 1.2 Goals of the Dissertation Thesis

Together with my supervisors, we aimed to contribute to effective, efficient, and easy-touse countermeasures against passive non-invasive side-channel attacks. Our goals can be summarized as follows:

- 1. Development of effective, efficient (in the terms of area and time), and easy-touse side-channel countermeasures for symmetric cryptography (most notably Rijndael/AES) tailored specifically for FPGA hardware platforms.

- 2. Side-channel analysis of the Rainbow signature scheme and development of effective and efficient side-channel countermeasures for such multivariate quadratic signature schemes.

## 1.3 Structure of the Dissertation Thesis

This doctoral dissertation thesis is organized into 5 chapters as follows:

- *Chapter 1: Introduction*: Describes the motivation behind our efforts together with our goals.

- *Chapter 2: Background and State of the Art*: Introduces the reader to the necessary theoretical background and surveys the current state of the art.

- Chapter 3: Symmetric Cryptography: Describes our countermeasure development for PRESENT, Rijndael/AES, and Serpent on FPGA. Countermeasures for both register-transfer level and high level synthesis are proposed and thoroughly evaluated.

- Chapter 4: Asymmetric Cryptography: Describes our side-channel attack on the Rainbow signature scheme reference implementation and our development of a multiplatform countermeasure based on a concept of equivalent keys, suitable for multivariate-quadratic signature schemes.

- *Chapter 5: Conclusion*: Summarizes the results of our research, suggests possible topics for further research, and concludes the thesis.

# CHAPTER 2

## **Background and State of the Art**

This chapter was published as a review article in the Sensors journal [A.1] in 2022.

This chapter presents theoretical background and state of the art in the area of noninvasive passive side-channel attacks. It is structured into 7 sections as follows:

- 1. *Introduction to Side-Channel Security*: Introduces side-channel leakage origin, measurement setup, formal model of the leakage, and leakage functions.

- 2. Non-Profiled Attacks: Describes non-invasive passive non-profiled attacks.

- 3. Profiled Attacks: Describes non-invasive passive profiled attacks.

- 4. *Side-Channel Related Metrics*: Describes both experimental and theoretical attack-related metrics.

- 5. Countermeasures Against Attacks: Describes hiding and masking countermeasures.

- 6. Attacks on Protected Implementations: Describes extensions of the presented attacks for attacking implementations with countermeasures.

- 7. Leakage Assessment: Describes methods for evaluations of side-channel leakage.

### 2.1 Introduction to Side-Channel Security

Side channels of digital systems that may be used to compromise the system include power consumption [83, 49, 29, 40], electromagnetic radiation [136], combinational logic delay [150, 183], timing [84], and more. Some of these side channels are mutually dependent, for example, the relationship between current intensity and the magnetic field can be shown, e.g., by Biot–Savart law [160], and the combinational logic delay can be convincingly modeled as inversely proportional to the voltage drop [128]. This dissertation

#### 2. Background and State of the Art

thesis focuses on dynamic power consumption side channel, but presented concepts may be relevant for other side channels as well.

Side-channel attacks may be classified in many different ways [160], such as invasive/noninvasive or active/passive. Invasive attacks require depackaging the chip in order to access internal components, such as data buses, while non-invasive attacks only exploit the external access. Active attacks tamper with proper functionality of the device (e.g., by introducing faults), while passive attacks only make use of observation of the device during its undisturbed operation. This dissertation thesis focuses on non-invasive passive attacks only.

Side-channel attacks can also be classified as either horizontal or vertical. Horizontal attacks exploit leakage during a single algorithm execution, while vertical attacks exploit leakage from multiple executions. For example, considering a hardware implementation of RSA algorithm that uses naïve Square&Multiply exponentiation, either only Square is performed, or both Square&Multiply operations are performed during computation, for every exponent bit, depending on the bit being zero or one. This not only influences execution time, but, in some cases, it also allows the attacker to directly read the secret key from a single measured power/EM trace by graphing the trace, as the two operations form distinctive patterns [84]. This kind of a horizontal side-channel attack is called Simple Power Analysis. Unlike this simple example, this dissertation thesis focuses on vertical side-channel attacks, where the information is typically contained in the instantaneous signal amplitude as further described below.

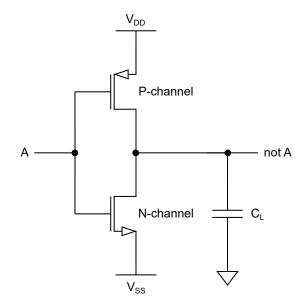

A CMOS inverter model is depicted in Figure 2.1. Three different dissipation sources can be observed in such a CMOS structure [137]:

- static leakage current,

- short-circuit current, and

- capacitance charge and discharge.

When the inverter input presents a stable voltage corresponding to 0 or 1, one of the transistors is open and the other one is closed. In this case, only static leakage current is present. When the input changes, short-circuit current can be observed for a brief period of time when both transistors are open. Furthermore, the modeled load capacitance  $C_L$  has to be charged to the proper voltage when the input changes its value. Therefore, based on the instantaneous current consumption, it can be easily distinguished whether a transition happened or not. This fact is exploited by the most common leakage models as described later in this section. The consumption during a transition is demonstrated in Figure 2.2.

Because the P-channel MOSFET majority carriers have lower mobility and the minority carriers have lower lifetime, in contrast to the N-channel MOSFET [71, 57], the P-channel MOSFET is typically built larger than the N-channel MOSFET [71], resulting in different characteristics, most importantly on-resistance and propagation delay (for non-inverter gates) [138]. Due to differences between N-channel and P-channel MOSFETs, the output value after transition can also be distinguished by the instantaneous current [100].

Figure 2.1: A CMOS inverter model.

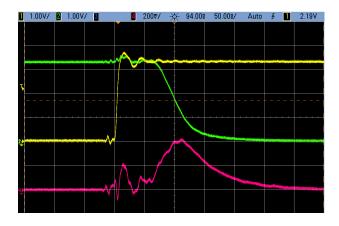

Figure 2.2: A CMOS inverter current consumption. The yellow line is the inverter input, the green line is the inverter output. The pink line is the current consumption, where peaks during the transition are clearly observable.

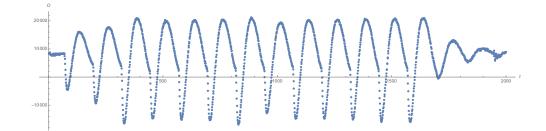

Figure 2.3: Rijndael/AES Encryption FPGA Power Trace.

This simple example illustrates data dependency of the instantaneous power consumption, which is the main cause of the power-related side-channel information leakage in CMOS-based integrated circuits. Vertical attacks exploiting this kind of leakage typically require multiple side-channel measurements, unlike the previously described simple power analysis attack.

#### 2.1.1 Measurements

The device's side channel is typically observed during a cryptographic operation, resulting in a measurement record, so-called trace, i.e., a vector of samples. For example, a single trace of dynamic power consumption during Rijndael/AES encryption in an FPGA is visualized in Figure 2.3. As mentioned earlier, multiple aligned traces, such as this one, are typically required for a successful attack, although single-trace attacks are sometimes also possible. This subsection briefly describes different measurement methods.

#### 2.1.1.1 Power Consumption

Power consumption of the cryptographic device is typically measured using an oscilloscope which samples voltage across a shunt resistor. The current can then be obtained, knowing both resistance and voltage, using Ohm's law  $I = \frac{U}{R}$ . However, raw ADC values corresponding to the voltage can be directly used in a typical attack scenario, since the current and the voltage are assumed to be linearly dependent, as long as the oscilloscope setup parameters are consistent during all measurements.

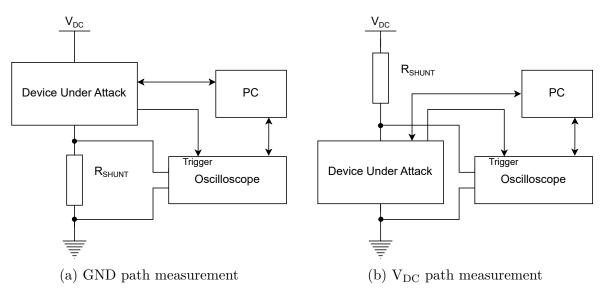

Various measurement setups are described in [115], the differences being primarily in the shunt resistor placement:

- Shunt resistor in GND path, with the voltage across the resistor being sampled by the oscilloscope, as shown in Figure 2.4a,

- Shunt resistor in  $V_{DC}$  path, with the voltage across the cryptographic device being sampled by the oscilloscope, as shown in Figure 2.4b, also observing voltage drops of the power regulator.

Figure 2.4: Example of a power measurement setup.

The latter setup offers an advantage when the device under attack has multiple power networks, because it allows the attacker to measure the just cryptographic core consumption. When the voltage is measured using a shunt resistor in the ground path (Figure 2.4a), the measured voltage typically contains more noise such as noise caused by the device's peripheral drivers. When measuring in the  $V_{DC}$  path (Figure 2.4b), the DC shift must be removed (unless measuring in a differential mode), which can be ensured either by using oscilloscope's AC mode, or by using external DC blocker. Other choices for power measurement include differential or current probes. However, these are not recommended unless necessary, as they present an additional source of environmental noise [115].

In a real-world attack, any decoupling capacitors near the cryptographic core must be removed as they might filter out the relevant voltage changes. Correct power measurement setup is crucial for successful side-channel analysis. Parameters such as the environmental noise, sampling rate, or synchronization jitter have a direct impact on the attack success [127].

#### 2.1.1.2 Electromagnetic Radiation

Similarly to power measurement, an oscilloscope connected to a near-field probe may be used for measurement of electromagnetic radiation [136]. As mentioned earlier, there is a close relationship between the power consumption and the radiation [160].

Attacking electromagnetic radiation offers more degrees of freedom compared to the power analysis. The attacker can examine a particular part of the chip only, and she can choose from a wide variety of probes. Consequently, EM analysis may provide a very powerful tool at the cost of more intricate and more costly employment. Further discussion of EM side channels is outside of the scope of this dissertation thesis.

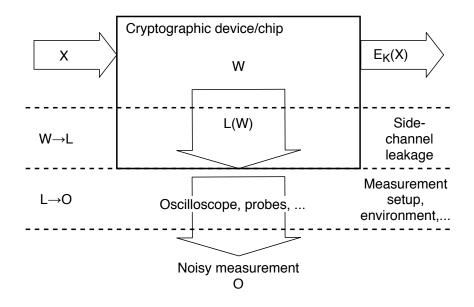

(b) Ring oscillator + asynchronous counter.

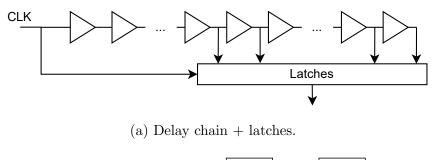

Figure 2.5: Combinatorial logic delay monitors.

In addition to directly measuring electromagnetic radiation of the device under attack, data-dependent leakage may also be unintentionally broadcast by a radio transmitter present on the same chip (such as SoC bluetooth/WiFi transmitters with built-in encryption) [36]. In mixed-signal systems on chip, the leakage from the digital part of the chip couples through substrate to the high-frequency analog radio transmitter [2]. This class of attacks is called screaming channels and it allows the attacker to successfully reveal cipher keys from traces obtained by a radio receiver from even 15 m distance [35].

#### 2.1.1.3 Combinational Logic Delay

Combinational logic delay inside a chip can be satisfactorily modeled as inversely proportional to the voltage drop of the internal power network [128], which is data-dependent due to the switching activity. In FPGA chips, the delay can be measured internally using a delay-chain monitor [61, 150], shown in Figure 2.5a, or using a ring oscillator monitor [183], shown in Figure 2.5b. Acquired delay traces can be used in side-channel analysis in a similar fashion as the power traces.

Furthermore, crosstalk between two long wires inside the chip can be detected [140] using a ring oscillator monitor as a receiver. In a multitenant FPGA chip setting, where independent customers share the same FPGA accelerator, e.g., in a cloud environment, these monitors open possibility for remote and even automated large-scale side-channel attacks.

#### 2.1.2 Formal Model

This subsection presents a formal model of side-channel leakage and corresponding terminology as described in [58, 163]. The presented model is used for attack descriptions in

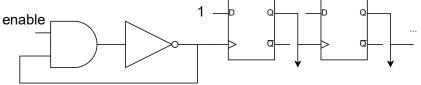

Figure 2.6: Illustration of channels involved in side-channel analysis.

following sections.

Consider a physical device performing a cryptographic operation  $E_k(x)$ , depending on a secret (sub)key  $k \in \mathcal{K}$ , where  $\mathcal{K} = \mathbb{B}^m = \{0, 1\}^m$ ,  $x \in \mathcal{X}$ . The unknown (sub)key is then modeled as a random variable  $\mathbf{K} : \Omega \to \mathcal{K}$ , the processed data as a random variable  $\mathbf{X} : \Omega \to \mathcal{X}$ .

Key-dependent state transitions (bit flips) occur inside the device during the execution of  $\mathbf{E}_k$ . These state transitions are described as word pairs  $(v_1, v_2) \in \mathcal{W}$ , where  $\mathcal{W} = \mathbb{B}^n \times \mathbb{B}^n$ ,  $v_1$  is previous state,  $v_2$  is new state. Unknown transitions (word pairs) are modeled as a random variable  $\mathbf{W} : \Omega \to \mathcal{W}$ .

State transitions  $\mathbf{W}$  induce side-channel leakage  $\mathbf{L}$  on space  $\mathcal{L}$ , modeled by a sidechannel leakage function  $\mathsf{L}(\mathbf{W})$ . Leakage  $\mathbf{L}$  is measured through the noisy physical observable  $\mathbf{O}$  on space  $\mathcal{O}$ .

The model describes a cascade of two channels  $\mathbf{W} \to \mathbf{L} \to \mathbf{O}$ . This cascade is comprised of a leakage channel  $\mathbf{W} \to \mathbf{L}$  through which information on processed words  $\mathbf{W}$  leaks in  $\mathbf{L}$ , and observation channel  $\mathbf{L} \to \mathbf{O}$  through which the attacker obtains noisy information on  $\mathbf{L}$ . The described channels are illustrated in Figure 2.6.

Observing **O** then means measuring  $q \in \mathbb{N}^+$  traces  $o_{x_i}(t)$ , i = 1, 2, ..., q, of device's side channel (e.g., power consumption)  $\mathbf{O}(t)$ , while processing known data  $x_i$ . In case of Rijndael/AES,  $o_{x_i}$  might be a trace similar to the one in Figure 2.3 and  $x_i$  might be a corresponding plaintext or ciphertext block.

Side-channel attack is then defined as determining the (sub)key k by reconstructing the words **W** and using information on **L** contained in **O**. For example, the attack may be performed in these steps:

1. The real leakage function L is unknown, so the attacker assumes a hypothetical

#### 2. BACKGROUND AND STATE OF THE ART

leakage function  $\hat{\mathsf{L}}$  (described in subsection 2.1.3).

- 2. The attacker makes a guess  $\hat{k} \in \mathcal{K}$  on the real (sub)key k.

- 3. Based on the known data  $\mathbf{X}$ , she computes an intermediate value  $f_{\hat{k}}(\mathbf{X})$  within the  $\mathbf{E}_{\mathbf{k}}$  computation.

- 4. The intermediate value implies a guess  $\mathbf{W}_{\hat{k}}$ , which in turn implies a guess  $\hat{\mathbf{L}}_{\hat{k}} = \hat{\mathsf{L}}(\mathbf{W}_{\hat{k}})$ .

- 5. Finally, the attacker checks if the guess  $\hat{\mathbf{L}}_{\hat{k}}$  is compatible with the observed **O**.

This attack scenario assumes that the real (sub)key k is fully enumerable in a reasonable time and space. As shown in section 2.2 and section 2.3, side-channel attacks typically target a single subkey, e.g., an octet in case of Rijndael/AES.

#### 2.1.3 Leakage Function

Side-channel attacks can be classified into two groups according to approach to the hypothetical leakage function  $\hat{L}$ :

- Non-profiled attacks, where the attacker only makes use of an explicit leakage function, which is effective for a range of devices (e.g., based on CMOS technology) instead of being tailored for a specific one.

- **Profiled attacks**, which consist of a profiling step, where the attacker examines a duplicate of the device under attack and she creates her own leakage approximation. Furthermore, her approximation inherently takes noise contained in **O** into account, making her empirical model more effective. This model is used for the attack, while an explicit leakage function may or may not be used during the process.

Besides the differences regarding approach to the hypothetical leakage function, these two types of attacks also assume a differently powerful attacker: for a profiled attack, an exact duplicate of the device under attack is required, whereas it is not for a nonprofiled attack.

This subsection briefly introduces widely used explicit leakage functions necessary for non-profiled attacks which are discussed thereafter in section 2.2. Profiled attacks are discussed later in section 2.3.

#### 2.1.3.1 Hamming distance and Hamming weight

Hamming distance leakage function for  $v_1, v_2 \in \mathbb{B}^n$  is defined as a number of bit positions at which the words  $v_1, v_2$  differ [29]:

$$\hat{\mathsf{L}}^{\mathrm{HD}}(v_1, v_2) = \mathrm{HD}(v_1, v_2) \in \mathcal{L} = \{0, 1, ..., n\},$$

(2.1)

The function corresponds to the number of bit flips in an *n*-bit wide register during  $(v_1, v_2)$  transition. It is a generally applicable model suitable for attacking CMOS logic. Hamming distance is equal to Hamming weight of XOR of the operands:  $HD(v_1, v_2) = HW(v_1 \oplus v_2)$ , where Hamming weight HW is defined as a number of bits in the word that are set to one.

When  $v_1$  is a zero vector, the Hamming distance leakage function reduces to Hamming weight leakage function [111]

$$\hat{\mathsf{L}}^{\mathrm{HW}}(v_2) = \mathrm{HW}(v_2) \in \mathcal{L} = \{0, 1, ..., n\},$$

(2.2)

for  $v_2 \in \mathbb{B}^n$ . This is often the case when attacking software implementations in microcontrollers [83, 125].

Assuming Hamming weight  $HW(x), x \in \mathbb{B}^n$  and uniformly distributed values of n bits in a word  $x \in \mathbb{B}^n$ , following properties hold for Hamming weight (and consequently Hamming distance):

$$\mathrm{HW}(x) \sim \mathrm{Binom}(n, \frac{1}{2}), \tag{2.3}$$

$$\mathbb{E}(\mathrm{HW}(x)) = \frac{n}{2}, \ \mathrm{Var}(\mathrm{HW}(x)) = \frac{n}{4}.$$

(2.4)

Furthermore, the Binomial distribution can be satisfactorily approximated by the Normal distribution for  $p = \frac{1}{2}$  [77] and therefore

$$\mathrm{HW}(x) \approx \mathcal{N}(\frac{n}{2}, \sqrt{\frac{n}{4}}). \tag{2.5}$$

**Generalized distance model** Less commonly, different weights may be assigned for  $0 \rightarrow 1$  and  $1 \rightarrow 0$  transitions, resulting in a generalized distance leakage function. E.g., weight 1.5 may be used instead of 1 for the  $1 \rightarrow 0$  transition to provide a more effective attack on some platforms [96].

#### 2.1.3.2 Identity

Identity leakage function [58]

$$\hat{\mathsf{L}}^{\mathrm{id}}(f_{\hat{k}}(x_i)) = f_{\hat{k}}(x_i) \in \mathcal{L}, \qquad (2.6)$$

for  $x_i \in \mathcal{X}$ , is equal to the targeted intermediate value within the  $E_k(x_i)$  computation. It is the most general leakage function in the sense that it puts no assumptions on the cryptographic device or technology.

### 2.2 Non-Profiled Attacks

Non-profiled attacks can be divided into:

- **Parametric/Moment-based attacks**, which exploit statistical moments (such as mean or variance). Typical examples include Differential Power Analysis [83] or Correlation Power Analysis [49, 29].

- Non-parametric/Information-theoretic attacks, which exploit the entire underlying statistical distribution. A typical example is Mutual Information Analysis [58].

- Machine learning-based attacks, namely the Deep Learning Power Analysis [166].

These attacks are presented in more depth in this section.

Unless stated otherwise, all of the attack descriptions in this section assume the attacker has already acquired  $q \in \mathbb{N}^+$  traces  $o_{x_i}(t)$ , i = 1, 2, ..., q, of device's side channel  $\mathbf{O}(t)$ (e.g., power consumption), while processing known data  $x_i$  (e.g., plaintext), where bits in  $x_i$  are uniformly distributed. Usage of uniform plaintext gives a good confidence about uniformity of intermediate values during the computation, since a cipher where properties such as diffusion are expected is typically targeted.

The q measured traces can be modeled as q samples from a multivariate random variable O(t), where the dimension of the variable corresponds to a number of sampling points within single trace. All the attacks presented in this section, except for the last one, are univariate, i.e., only a single point in time is examined, which is desirable when the sensitive intermediate value manifests itself at a single time instant. In this section, unless stated otherwise, it is assumed that the interesting time instant  $t = \tau$  is known and only the single relevant sampling point is considered. The q measured traces are therefore considered an univariate random variable  $O(\tau)$ .

In practice, when the time instant is unknown, the attack is performed at every time instant t independently. The final attack evaluation thus typically requires more attention and skill due to a larger false-result chance. Alignment of the traces is required when synchronization of the measurements (e.g., using a trigger signal) is not possible.

#### 2.2.1 Differential Power Analysis (DPA)

The Differential Power Analysis [83] attack is performed in these steps:

- 1. Assume a single bit (n = 1) Hamming weight (or distance) leakage function L.

- 2. Enumerate (sub)key guesses  $\hat{k} \in \mathcal{K}$ .

- 3. Compute an intermediate value  $v_2 = f_k(x_i), \forall k, x_i$  (and the previous state  $v_1$  if Hamming distance is used) and consider only a single bit (e.g., the LSB).

- 4. For every guess  $\hat{k}$ , partition measurements  $o_{x_i}$  into two groups  $O_0^{\hat{k}}, O_1^{\hat{k}}$  according to the leakage function  $\hat{L}$ :

$$O_0^k = \{ o_{x_i} | \hat{\mathsf{L}}(v_1, f_{\hat{k}}(x_i)) = 0 \},$$

(2.7)

$$O_1^k = \{ o_{x_i} \mid \hat{\mathsf{L}}(v_1, f_{\hat{k}}(x_i)) = 1 \}.$$

(2.8)

12

- 5. Select the guess  $\hat{k}$  for which the groups'  $O_0^{\hat{k}}, O_1^{\hat{k}}$  means differ the most.

- For wrong guesses  $\hat{k}$ , the traces for which L = 0 and the traces for which L = 1 are theoretically uniformly distributed in both groups.

- For the right guess  $\hat{k}$ , the groups  $O_0^{\hat{k}}, O_1^{\hat{k}}$  should be distinguishable by their mean value, due to the bias caused by the fixed bit.

In the last step, the original Kocher's DPA [83] selects the guess k for which the absolute difference of means between the two groups is greatest. More formally, the hypothesis about equal means may be examined by using Welch's *t*-test or a similar statistic.

#### Example: Attacking first round of Rijndael/AES

- 1. Assume Hamming weight or identity single-bit leakage (Hamming weight is equivalent to identity for n = 1).

- 2. Select an enumerable key-dependent intermediate value during Rijndael/AES encryption:  $f_{\hat{k}}(x_i) := \text{Sbox}(x_i \oplus \hat{k})$ . Sbox is an 8-bit bijection,  $f_{\hat{k}}(x_i)$  is therefore computable for each byte independently of the other bytes.

- 3. Enumerate byte subkey guesses  $\hat{k} \in \mathcal{K} = \{0, 1, \dots, 255\}$ , compute the intermediate value  $v_2 = f_{\hat{k}}(x_i), \forall \hat{k}, x_i$  and choose, e.g., the LSB.

- 4. Use the Hamming weight of the LSB as leakage function and partition traces  $o_{x_i}$  to groups  $O_0^{\hat{k}}, O_1^{\hat{k}}$ .

- 5. Select the subkey guess  $\hat{k}$  for which the two groups differ the most.

Because DPA builds its hypothesis on a single bit value, its assumptions regarding the leakage are very general. This may be one of the reasons for false results, so-called "ghost peaks". The choice of the bit in  $f_{\hat{k}}(x_i)$  has direct impact on the attack success. These facts are a motivation for multi-bit DPA as described further [20, 37].

#### 2.2.2 Multi-bit DPA and Partitioning Power Analysis (PPA)

Bevan's approach to multi-bit extension of the DPA is performing the original DPA independently for different bits of intermediate value  $f_{\hat{k}}(x_i)$  and summing all the independent differences of means [20]. Then the subkey guess with the greatest summed difference is selected. This approach reduces the number of traces necessary as well as the chance of a false result [20].

Messerges's multi-bit extension of the original DPA suggests using *n*-bit Hamming weight or Hamming distance leakage model [111], therefore utilizing the whole  $f_{\hat{k}}(x_i)$  value. This time, two sets  $O_{<}^{\hat{k}}$ ,  $O_{\geq}^{\hat{k}}$  are defined so that

$$O_{<}^{\hat{k}} = \{ o_{x_i} \, | \, \hat{\mathsf{L}}(f_{\hat{k}}(x_i)) < \frac{n}{2} \}, \tag{2.9}$$

13

#### 2. Background and State of the Art

$$O_{\geq}^{\hat{k}} = \{ o_{x_i} \, | \, \hat{\mathsf{L}}(f_{\hat{k}}(x_i)) \ge \frac{n}{2} \}, \tag{2.10}$$

and their difference is examined similarly to the original DPA.

Partitioning Power Analysis [4, 90] is a generalization of the multi-bit DPA. Assuming an *n*-bit  $f_{\hat{k}}(x_i)$  intermediate value and a Hamming weight or Hamming distance leakage function, the traces  $o_{x_i}$  are partitioned into (n + 1) sets  $O_0^{\hat{k}}, \ldots O_n^{\hat{k}}$  so that

$$O_j^k = \{ o_{x_i} | \hat{\mathsf{L}}(f_{\hat{k}}(x_i)) = j \}.$$

(2.11)

The distinguishing statistic (which is a difference of means in the original DPA) is then defined by using weights  $a_j \in \mathbb{R}$  as

$$\sum_{j=0}^{n} a_j \cdot \mu_{O_j^{\hat{k}}},\tag{2.12}$$

where  $\mu_{O^{\hat{k}}}$  are means of the aforementioned groups.

The original DPA is a special case of 1-bit PPA where  $a_0 = -1, a_1 = 1$ . Bevan's 4-bit DPA is a special case of 4-bit PPA where  $a_0 = -\frac{1}{8}, a_1 = -\frac{1}{4}, a_2 = 0, a_3 = \frac{1}{4}, a_4 = \frac{1}{8}$ . Messerges's n-bit DPA is a special case of n-bit PPA where  $a_j = -1$  for  $0 \le j < \frac{n}{2}$ , and  $a_j = 1$  for  $\frac{n}{2} \le j \le n$  [90].

#### 2.2.3 Correlation Power Analysis (CPA)

The Correlation Power Analysis [49, 29] attack is performed in these steps:

- 1. Assume a Hamming weight or Hamming distance leakage function  $\hat{\mathsf{L}}$ .

- 2. Enumerate (sub)key guesses  $\hat{k} \in \mathcal{K}$ .

- 3. Compute an intermediate value  $v_2 = f_{\hat{k}}(x_i), \forall \hat{k}, x_i$  (and the previous state  $v_1$  if using Hamming distance).

- 4. For every key guess  $\hat{k}$ , pairs  $(o_{x_i}, \hat{\mathsf{L}}(v_1, f_{\hat{k}}(x_i)))$  represent samples from joint distribution  $(\mathbf{O}, \hat{\mathbf{L}}_{\hat{k}})$ .<sup>1</sup>

- 5. Compute Pearson correlation coefficient  $\rho_{\hat{k}} = \frac{\text{Cov}(\mathbf{O}, \hat{\mathbf{L}}_{\hat{k}})}{\sigma_{\mathbf{O}}\sigma_{\hat{\mathbf{L}}_{\hat{k}}}}$  for every  $\hat{k}$ .

- 6. Select the guess  $\hat{k}$  for which the value of  $|\rho_{\hat{k}}|$  is the highest.

Assuming there is a linear dependence between the predicted leakage and the physical observation, a significant correlation  $\rho_{\hat{k}}$  should appear for the right guess  $\hat{k}$ , while for a wrong guess, the  $\rho_{\hat{k}}$  should converge to zero.

<sup>&</sup>lt;sup>1</sup>In other words, every trace is paired with the predicted Hamming weight/distance.

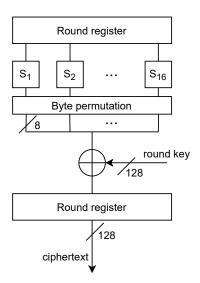

Figure 2.7: Architecture of Rijndael/AES last round. The scheme is unrolled for illustration purposes only, both "Round register" blocks depict the same hardware register.

#### Example: Attacking last round of Rijndael/AES

- 1. Assume the architecture illustrated in Figure 2.7 and a Hamming distance leakage (both  $v_1, v_2$  must be derived). Let  $\mathbf{Y} = \mathbf{E}_k(\mathbf{X})$ , i.e., ciphertext.

- 2. Let  $v_2 = y_i$ . The previous register state is then  $v_1 = f_{\hat{k}}(y_i) = \text{Sbox}^{-1}(\text{Perm}^{-1}(y_i \oplus \hat{k}))$ . Both values are once again enumerable for each byte independently of the other bytes due to the fact that the MixColumns operation is not performed in the last round.

- 3. Enumerate byte subkey guesses  $\hat{k} \in \mathcal{K} = \{0, 1, ..., 255\}$ , and compute the intermediate value  $f_{\hat{k}}(y_i), \forall \hat{k}, y_i$ .

- 4. Compute the leakage function  $\hat{\mathsf{L}}^{\mathrm{HD}}(f_{\hat{k}}(y_i), y_i), \forall \hat{k}, y_i$ .

- 5. Compute Pearson correlation coefficient  $\rho_{\hat{k}} = \frac{\text{Cov}(\mathbf{O}, \hat{\mathbf{L}}_{\hat{k}})}{\sigma_{\mathbf{O}}\sigma_{\hat{\mathbf{L}}_{\hat{k}}}}$  for every  $\hat{k}$ .

- 6. Select the guess  $\hat{k}$  for which the value of  $|\rho_{\hat{k}}|$  is the highest.

Unlike previously described DPA attacks, which use a partitioning approach, the CPA attack uses a comparative approach. However, CPA with a single-bit leakage function is equivalent to the original DPA. Interestingly, CPA is equivalent to normalized PPA with weights implicitly given by the distribution of bits in  $f_{\hat{k}}(x_i)$ . For a uniform distribution of bits in  $f_{\hat{k}}(x_i)$ , CPA is equivalent to the Bevan's multi-bit DPA [90].

The CPA attack assumes a linear relationship between the predicted leakage and the physical observation. However, this requirement can be relaxed to monotonicity by using

the Spearman coefficient instead of the Pearson coefficient [14]. Similar to DPA, CPA exploits statistical moments such as mean or covariance, and therefore requires a "normally" distributed observation channel. The success of the attack largely depends on the quality of the leakage approximation and present noise.

#### 2.2.4 Mutual Information Analysis (MIA)

The Mutual Information Analysis [58] attack is performed in these steps:

- 1. Assume an arbitrary leakage function  $\hat{L} \in \mathcal{L}$  (with some restrictions, as explained in subsubsection 2.2.4.1).

- 2. Enumerate (sub)key guesses  $\hat{k} \in \mathcal{K}$ .

- 3. Compute an intermediate value  $v_2 = f_{\hat{k}}(x_i), \forall \hat{k}, x_i$  (and the previous state  $v_1$  if using Hamming distance).

- 4. Let  $L_0, \ldots, L_l$  be subsets of  $\mathcal{L}$  so that the set  $\{L_0, \ldots, L_l\}$  is a partitioning of  $\mathcal{L}$ . The elements  $L_j, j = 0, \ldots, l$ , are called atoms.

- 5. Associate inputs  $x_i$  that leak  $L_i$  under key guess  $\hat{k}$  to  $L_i^{\hat{k}}$ :

$$L_{j}^{\hat{k}} = \{ x_{i} \mid \hat{\mathsf{L}}(v_{1}, f_{\hat{k}}(x_{i})) \in L_{j} \}.$$

(2.13)

Each partition  $\{L_0^{\hat{k}}, ..., L_l^{\hat{k}}\}$  induces a subdivision of measurements  $o_{x_i}$ .

- 6. Define conditional distributions  $\{\mathbb{P}_{\mathbf{O}|L_{j}^{\hat{k}}}\}_{j=0}^{l}$  by using the subdivision of  $\mathbf{O}$ , and let  $\mathbb{P}_{\mathbf{O}}, \mathbb{P}_{\mathbf{L}_{\hat{k}}}$  be probability distributions of  $\mathbf{O}, \hat{\mathbf{L}}_{\hat{k}}$ .

- 7. Select  $\hat{k}$  with the highest mutual information  $\mathbf{I}(\hat{\mathbf{L}}_{\hat{k}}; \mathbf{O})$ .

Unlike DPA or CPA, the Mutual Information Analysis exploits mutual information, which is defined as

$$\mathbf{I}(\mathbf{X};\mathbf{Y}) = D_{KL}(\mathbb{P}_{\mathbf{X},\mathbf{Y}} || \mathbb{P}_{\mathbf{X}} \otimes \mathbb{P}_{\mathbf{Y}}), \qquad (2.14)$$

where  $D_{KL}$  is Kullback-Leibler divergence, i.e., a statistical distance describing probability distribution difference. Mutual information is directly related to entropy H:

$$\mathbf{I}(\mathbf{X};\mathbf{Y}) = \mathbf{H}(\mathbf{X}) - \mathbf{H}(\mathbf{X}|\mathbf{Y}) = \mathbf{H}(\mathbf{X}) + \mathbf{H}(\mathbf{Y}) - \mathbf{H}(\mathbf{X},\mathbf{Y}) = \mathbf{I}(\mathbf{Y};\mathbf{X}), \quad (2.15)$$

where  $H(\mathbf{X}|\mathbf{Y})$  is conditional entropy,  $H(\mathbf{X}, \mathbf{Y})$  is joint entropy. Mutual information can be intuitively interpreted as the amount of information obtained about  $\mathbf{X}$  by observing  $\mathbf{Y}$ or, in other words, the reduction of uncertainty in  $\mathbf{X}$  obtained by observing  $\mathbf{Y}$ .

The mutual information computation may go as follows:

1. Using measurements  $o_{x_i}$  belonging to  $L_j^{\hat{k}}$ , estimate the conditional distribution  $\mathbb{P}_{\mathbf{O} \mid L_j^{\hat{k}}}$ and the conditional entropy  $\tilde{\mathrm{H}}(\mathbf{O} \mid \hat{\mathbf{L}}_{\hat{k}} = j)$ .

- 2. Compute the conditional entropy  $\tilde{H}(\mathbf{O}|\mathbf{\hat{L}}_{\hat{k}})$  by using  $\{\tilde{H}(\mathbf{O}|\mathbf{\hat{L}}_{\hat{k}}=j)\}_{j=0}^{l}$ .

- 3. By using all of the measurements  $o_{x_i}$ , estimate the distribution  $\mathbb{P}_{\mathbf{O}}$  and the entropy  $\tilde{\mathrm{H}}(\mathbf{O})$ .

- 4. Compute the mutual information  $\tilde{\mathbf{I}}(\hat{\mathbf{L}}_{\hat{k}}; \mathbf{O}) = \tilde{\mathrm{H}}(\mathbf{O}) \tilde{\mathrm{H}}(\mathbf{O}|\hat{\mathbf{L}}_{\hat{k}}).$

#### Example: Attacking AES/Rijndael with minimum assumptions

- 1. Assume an identity leakage function  $\hat{\mathsf{L}}(f_{\hat{k}})$ , e.g., three MSBs of  $f_{\hat{k}}(x_i) = \mathrm{Sbox}(x_i \oplus \hat{k})$

- 2. Enumerate byte subkey guesses  $\hat{k} \in \mathcal{K} = \{0, 1, \dots, 255\}$ , and compute the intermediate value  $f_{\hat{k}}(x_i), \forall \hat{k}, y_i$ .

- 3. For every subkey guess, associate each  $o_{x_i}$  with an atom of  $\{L_i^{\hat{k}}\}_{i=0}^7$  based on its input's predicted leakage.

- 4. For every subkey guess, estimate the densities  $\mathbb{P}_{\mathbf{O}}$  and  $\mathbb{P}_{\mathbf{O}|\hat{\mathbf{L}}_{\hat{k}}}$  and compute the mutual information  $\tilde{\mathbf{I}}(\hat{\mathbf{L}}_{\hat{k}};\mathbf{O})$ .

- 5. Select  $\hat{k}$  with the highest mutual information  $\tilde{\mathbf{I}}(\hat{\mathbf{L}}_{\hat{k}}; \mathbf{O})$ .

Crucial aspect of Mutual Information Analysis is the estimation of probability densities  $\mathbb{P}_{\mathbf{O}}$  and  $\mathbb{P}_{\mathbf{O}|\hat{\mathbf{L}}_{t}}$ . Some of the choices include:

- histogram, i.e., a non-parametric discrete estimate;

- kernel density estimate, i.e., a non-parametric continuous estimate; and

- finite mixture model, i.e., a (semi-)parametric continuous estimate.

The quality of the estimate has a direct influence on both attack success and computational complexity [173, 15].

A histogram provides a simple and efficient estimate with the most critical parameter being the number of bins [173]. The best estimate would require as many bins as there are values in the domain; however, it would be problematic to get enough values in every bin for it to be statistically significant. Less bins result in less information, but also lower susceptibility to noise. The original MIA [58] proposes using l + 1 bins, i.e., as many bins as there are atoms in the  $\mathcal{L}$  partitioning.

A kernel density estimate provides better attack results than the histogram [173] at the cost of its higher computational complexity. In this case, the kernel and bandwidth are the most critical parameters. Popular kernel choices include Epanechnikov (which is mean-square-error optimal) and Gaussian (for its convenience). Bandwidth has a similar role as bins in histograms, and it can be intuitively seen as a "smoothing parameter". Generally speaking, the attacker aims to select the bandwidth as small as allowed by the data. A "rule-of-thumb" bandwidth estimator can be used alongside the Gaussian kernel [157].

A finite mixtures model assumes the underlying distribution to be a mixture of distributions, whose parameters are estimated, e.g., by using the expectation-maximization algorithm. Typically, a mixture of Gaussians is assumed [92].

Mutual information analysis puts no hard assumptions on the leakage function or the underlying distributions and provides sound results even with a simple identity leakage function. It provides a generic and powerful side-channel distinguisher (although it is less efficient in scenarios well-suited for DPA/CPA) [173, 15, 175].

#### 2.2.4.1 Leakage Function in Partitioning Attacks

Mutual Information Analysis allows for an arbitrary leakage function, giving the attacker a great degree of freedom. Although Hamming weight or Hamming distance leakage functions may be used when it is possible to predict both  $v_1, v_2$ , their usage inherently leads to a loss of information. Identity leakage function, which is much more generic, may also be used. If the Hamming weight/distance estimate is possible, identity is shown to be less efficient, but still effective [173].

The leakage function must be selected so that a different  $\hat{k}$  must not yield a permutation of  $\hat{\mathbf{L}}_{\hat{k}}$ . For example, assume that using the identity of Rijndael/AES bijective S-box output. Different  $\hat{k}$  then leads to a permutation of  $\{L_0^{\hat{k}}, \ldots, L_l^{\hat{k}}\}$ , which means that the mutual information is constant and independent of  $\hat{k}$  [58]. This limitation can be easily overcome, e.g., by choosing only seven least significant bits of the Sbox output, or by using a Hamming weight/distance [58].

This problem does not only pertain to MIA, but to every partitioning attack (all the presented non-profiled attacks except CPA). When  $f_{\hat{k}}(x_i)$  is an injective function, an attack using trivial partitioning where each value belongs in its distinct class will always fail [162, 178].

#### 2.2.5 Kolmogorov–Smirnov Analysis (KSA)

The Kolmogorov–Smirnov Analysis [173, 177] attack is performed in these steps:

- 1.-6. The first six steps are same as for Mutual Information Analysis in subsection 2.2.4. Define the conditional distributions  $\{\mathbb{P}_{\mathbf{O}|L_{i}^{k}}\}_{j=0}^{l}$  and the distribution  $\mathbb{P}_{\mathbf{O}}$ .

- 7. For every  $\hat{k}$ , compute the average Kolmogorov–Smirnov distance between  $\mathbb{P}_{\mathbf{0}}$  and  $\mathbb{P}_{\mathbf{0}|L_{j}^{\hat{k}}|}$ , optionally further normalized by  $\frac{1}{|O_{L_{j}^{\hat{k}}|}|}$ , where  $|O_{L_{j}^{\hat{k}}}|$  is a size of the measurements set belonging to atom  $L_{j}^{\hat{k}}$ :

$$\mathbb{E}_{j}\left(\frac{1}{|O_{L_{j}^{\hat{k}}}|}D_{KS}(\mathbb{P}_{\mathbf{O}} || \mathbb{P}_{\mathbf{O} | L_{j}^{\hat{k}}})\right).$$

$$(2.16)$$

18

8. Select the key guess  $\hat{k}$  with the largest average KS-distance.

The Kolmogorov–Smirnov distance between  $\mathbb{P}_{\mathbf{X}}$  and  $\mathbb{P}_{\mathbf{Y}}$  is defined as

$$D_{KS}(\mathbb{P}_{\mathbf{X}} || \mathbb{P}_{\mathbf{Y}}) = \sup_{x} |F_{\mathbf{X}}(x) - F_{\mathbf{Y}}(x)|, \qquad (2.17)$$

where  $F_{\mathbf{X}}$  is a cumulative density function of  $\mathbf{X}$ . The Kolmogorov–Smirnov Analysis is heavily inspired by the Mutual Information Analysis. However, instead of estimating probability density function, the easier-to-obtain cumulative density function is used.

Alternatively, interclass Kolmogorov–Smirnov Analysis (iKSA) [98] distinguishes the key guess using the distance between the conditional distributions:

$$\frac{1}{2} \mathop{\mathbb{E}}_{j,j'} (D_{KS}(\mathbb{P}_{\mathbf{O} \mid L_j^{\hat{k}}} \mid\mid \mathbb{P}_{\mathbf{O} \mid L_{j'}^{\hat{k}}})).$$

(2.18)

Other choices for comparison of the distributions include Cramér–von Mises criterion or different F-divergences [173].

The Kolmogorov–Smirnov Analysis shares some important characteristics with MIA, as both attacks can be used with an identity leakage function, and therefore without precise knowledge about the implementation and leakage. It can provide better results for weak signals than MIA due to its noise robustness [177], and since it utilizes CDF instead of PDF, it may be more convenient.

#### 2.2.6 Differential Deep Learning Analysis (DDLA)

The Differential Deep Learning Analysis [166] attack is performed in these steps:

- 1. Assume an arbitrary leakage function  $\hat{L} \in \mathcal{L}$ .

- 2. Enumerate (sub)key guesses  $\hat{k} \in \mathcal{K}$ .

- 3. Compute an intermediate value  $v_2 = f_k(x_i), \forall \hat{k}, x_i$  (and the previous state  $v_1$  if using the Hamming distance).

- 4. Create labeled training datasets  $\{(o_{x_i}, \hat{\mathsf{L}}(v_1, f_{\hat{k}}(x_i)))\}_{\hat{k}}, \forall \hat{k}, o_{x_i}$ . Note that the same limitations as described in subsubsection 2.2.4.1 apply.

- 5. Perform Deep Learning classifier training for every dataset.

- 6. Select the key guess  $\hat{k}$  with the best DL training metrics.

Unlike the previously described attacks in this section, the Differential Deep Learning Analysis is typically used in a multivariate fashion, not univariate. In other words, the attack is not performed at a single sampling point/all the sampling points in the trace independently. Instead, the classifier is fed with the multivariate vectors corresponding to the entire encryption.

#### 2. Background and State of the Art

The Differential Deep Learning Analysis is a partitioning attack, like all the previously presented attacks except CPA. A key-dependent partitioning of the data is created and then the distinguishability of the partitions is examined by using the classifier. For the correct key guess, the classifier should be able to learn distinctive features of differently labeled data. When a wrong guess is made, the traces are randomly distributed across labels, and therefore the training metrics should be significantly worse than for the correct guess. Different training metrics are proposed for the final selection of the key, e.g., by using sensitivity analysis [166].

Various deep-learning architectures, such as a multilayer perceptron or a convolutional network may be used for the classifier. Translation-invariance property of convolutional networks can be exploited to attack desynchronized traces [34, 166], whereas previously described attacks would require synchronization of the traces during preprocessing, e.g., by using autocorrelation, due to their univariate nature. A distinct disadvantage of using the machine-learning based blackbox approach is limited explainability of the results [171].

### 2.3 Profiled Attacks

Profiled attacks assume the attacker has a fully-controlled identical copy of the device under attack at her disposal. She is capable of observing the device's side channels during execution of the identical cryptographic implementation. Moreover, she is able to feed the implementation with arbitrary inputs and keys. Her attack is tailored for a specific device and therefore more effective and efficient than a non-profiled attack.

Profiled attack consists of two phases:

- 1. **Profiling phase**, during which an empirical model of the leakage is created using the identical copy of the device under attack.

- 2. Attack phase, during which observations of the device under attack are evaluated using the previously profiled model.

Unlike non-profiled attacks presented in section 2.2, all the presented profiled attacks are multivariate, i.e., full traces O(t) are considered, where the dimension (t) corresponds to a number of sampling points within a single trace.

#### 2.3.1 Template Attack (TA)

The Template attack [40, 143] is performed in these steps:

1. Consider an arbitrary leakage function  $\hat{L} \in \mathcal{L}$ .

#### Profiling phase

2. Measure a profiling set of traces  $o_{(x_i,k_i)}(t)$  using desired (typically, but not necessarily random uniform) inputs  $(x_i, k_i)$ .

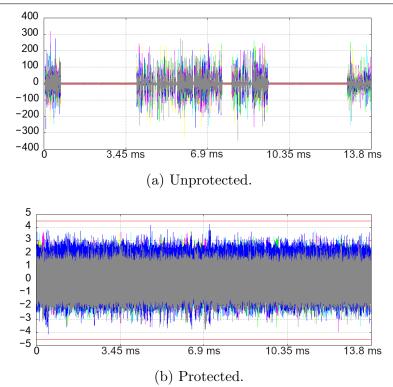

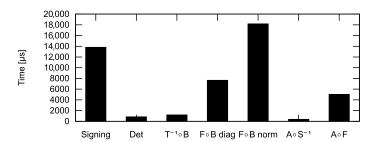

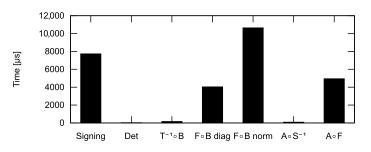

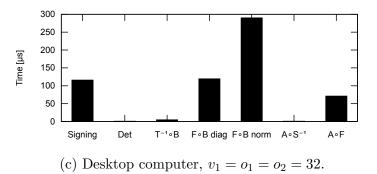

- 3. Compute an intermediate value  $v_2 = f_{k_i}(x_i), \forall k_i, x_i$  (and the previous state  $v_1$  if using Hamming distance).