## **Abstraction-Based Machine-Code Program Verification**

by

Ing. Jan Onderka

A dissertation thesis submitted to the Faculty of Information Technology, Czech Technical University in Prague, in partial fulfilment of the requirements for the degree of Doctor.

Doctoral study programme: Informatics Department of Digital Design

Prague, August 2024

#### Supervisor:

doc. Dipl.-Ing. Dr. techn. Stefan Ratschan Department of Digital Design Faculty of Information Technology Czech Technical University in Prague Thákurova 9

160 00 Prague 6

Czech Republic

Copyright © 2024 Ing. Jan Onderka

## **Abstract**

This dissertation thesis is focused on formal verification of machine-code systems using model checking with abstraction. The background and state of the art of machine-code model checking are presented, and weaknesses of previous approaches are noted. The author's research described in this dissertation thesis and previous conference proceedings articles presents novel solutions to the major problems of previous research: the systems are described in the Rust programming language and are inherently simulable, automatically converted to verification equivalents and verified within a novel framework based on Three-Valued Abstraction Refinement. Special care is taken to allow efficient verification of variables based on bit-vectors. The author has created a formal verification tool implementing the introduced techniques, and its performance is evaluated in the thesis. The tool can be used to verify arbitrary finite-state digital systems, with a special focus on systems with behaviour determined by machine-code programs. To the author's knowledge, the created tool is the first free, open-source, and publicly available tool of its kind.

#### **Keywords:**

Machine-code verification, translation of simulable descriptions, three-valued abstraction refinement, bit-vector domain

## **Abstrakt**

Tato disertační práce pojednává o formální verifikaci systémů založených na strojovém kódu pomocí techniky kontroly modelu s použitím abstrakce. Je prezentován současný stav poznání v tomto oboru a je poukázáno na slabá místa předchozích přístupů. Autorův výzkum popsaný v této disertační práci a předchozích článcích v konferenčních sbornících prezentuje nové způsoby řešení problémů předchozího výzkumu: systémy jsou popsány v programovacím jazyce Rust a samy o sobě simulovatelné, jsou automaticky konvertovány do verifikačních ekvivalentů a verifikovány v originální konstrukci založené na zjemňování trojhodnotové abstrakce. Pro účinnou verifikaci je speciálně zacházeno s proměnnými založenými na bitových vektorech. Autor práce vytvořil nástroj pro formální verifikaci, který implementuje představené techniky, a jeho schopnosti jsou v práci vyhodnoceny. Nástroj může být použit pro verifikaci libovolných konečných číslicových systémů, se zaměřením na systémy, kde je chování určeno programy ve strojovém kódu. Pokud je autorovi známo, vytvořený nástroj je první bezplatný a veřejně dostupný nástroj svého druhu s otevřeným zdrojovým kódem.

#### Klíčová slova:

Verifikace strojového kódu, překlad simulovatelných popisů, zjemňování trojhodnotové abstrakce, doména bitových vektorů

## **Acknowledgements**

I would like to thank my dissertation thesis supervisor Stefan Ratschan for his insight and support during my research. I would also like to thank the other academic and non-academic staff of the Department of Digital Design for their help with the formalities during the course of my studies. Finally, I thank my family for their support.

My research has been partially supported by the Grant Agency of the Czech Technical University in Prague, grant No. SGS20/211/OHK3/3T/18 and No. SGS23/208/OHK3/3T/18.

# **Contents**

| 1 | $\operatorname{Intr}$ | roduction                                                             | 1 |

|---|-----------------------|-----------------------------------------------------------------------|---|

|   | 1.1                   | Contribution                                                          | 2 |

|   | 1.2                   | Organisation of This Thesis                                           | 3 |

| 2 | Bac                   | ekground and State of the Art                                         | 5 |

|   | 2.1                   | Digital Systems                                                       | 6 |

|   |                       | 2.1.1 Digital System Levels                                           | 8 |

|   |                       | 2.1.2 Digital System Commonalities                                    | 0 |

|   |                       | 2.1.3 Formalisation as Moore Machines                                 | 1 |

|   | 2.2                   | Property Specifications                                               | 2 |

|   | 2.3                   | Formal Verification Using Model Checking                              | 4 |

|   |                       | 2.3.1 Classic Model-Checking Formalisms                               | 5 |

|   | 2.4                   | Advanced Techniques for Model Checking                                | 6 |

|   | 2.5                   | Abstraction and Abstraction Refinement                                | 8 |

|   |                       | 2.5.1 Methodologies                                                   | 9 |

|   |                       | 2.5.2 Abstraction Domains                                             | 0 |

|   | 2.6                   | State of the Art in Digital System Verification                       | 2 |

|   |                       | 2.6.1 Source-Code Systems                                             | 2 |

|   |                       | 2.6.2 Hardware Systems                                                | 3 |

|   |                       | 2.6.3 Machine-Code Systems                                            | 3 |

|   |                       | 2.6.4 Comparison of System Levels                                     | 5 |

|   | 2.7                   | Summary                                                               | 5 |

| 3 | Mac                   | chine-Code Verification Using Translation of Simulable Descriptions 2 | 7 |

| - | 3.1                   | Verification of Machine-Code Systems                                  |   |

|   | 3.2                   | Processor Descriptions                                                |   |

|   | 3.3                   | Subset of the Rust Language Usable in Descriptions                    |   |

|   | 3.4                   | Further Notes                                                         |   |

|   |                       |                                                                       |   |

## Contents

| 4 | Inp          | ut-base            | ed Three-valued Abstraction Refinement Framework                 | 37         |

|---|--------------|--------------------|------------------------------------------------------------------|------------|

|   | 4.1          | The N              | eed for a New Three-valued Abstraction Refinement Framework      | 37         |

|   | 4.2          | Previo             | ous Work on Three-valued Abstraction                             | 38         |

|   |              | 4.2.1              | Previous Frameworks and Their Problems                           | 40         |

|   | 4.3          | State-             | based and Input-based Refinement                                 | 40         |

|   | 4.4          | Input-             | based Abstraction Framework                                      | 42         |

|   |              | 4.4.1              | Generating Automata                                              | 42         |

|   |              | 4.4.2              | High-level View of the Input-based Framework                     | 43         |

|   | 4.5          | Sound              | ness, Monotonicity, and Completeness                             | 45         |

|   |              | 4.5.1              | Soundness Preservation through Modal Simulation                  | 47         |

|   |              | 4.5.2              | Proof of Soundness                                               | 49         |

|   |              | 4.5.3              | Proof of Monotonicity                                            | 49         |

|   |              | 4.5.4              | Proof of Completeness                                            | 50         |

|   | 4.6          | Impler             | mentation and Experimental Evaluation                            | 51         |

|   | 4.7          | Furthe             | er Notes                                                         | 53         |

| 5 | Δhs          | tract <sup>r</sup> | Three-valued Bit-vector Arithmetic                               | 55         |

| J | 5.1          |                    | ed Work                                                          | 56         |

|   | 5.2          |                    | Definitions                                                      | 57         |

|   | J.2          | 5.2.1              | Abstract Bit Encodings                                           | 57         |

|   |              | 5.2.2              | Abstract Transformers                                            | 58         |

|   |              | 5.2.3              | Algorithm Complexity Considerations                              | 59         |

|   |              | 5.2.4              | Naïve Universal Abstract Algorithm                               | 59         |

|   | 5.3          | -                  | l Problem Statement                                              | 60         |

|   | 5.4          |                    | lar Extreme-Finding Technique                                    | 60         |

|   | 5.5          |                    | Abstract Addition                                                | 63         |

|   | 5.6          |                    | Abstract Multiplication                                          | 64         |

|   |              | 5.6.1              | Obtaining a Best Abstract Transformer                            | 64         |

|   |              | 5.6.2              | At Most One Double-Unknown k-th Column Pair                      | 65         |

|   |              | 5.6.3              | Multiple Double-Unknown $k$ -th Column Pairs                     | 67         |

|   |              | 5.6.4              | Implementation Considerations                                    | 69         |

|   |              | 5.6.5              | Fast Abstract Multiplication Algorithm                           | 70         |

|   | 5.7          | Experi             | imental Evaluation                                               | 72         |

|   |              | 5.7.1              | Visualisation and Interpretation                                 | 72         |

|   | 5.8          | Furthe             | er Notes                                                         | 73         |

| 6 | Cre          | ated F             | ormal Verification Tool machine-check                            | <b>7</b> 5 |

| Ū | 6.1          |                    | based Three-valued Abstraction Refinement Using Abstraction Ana- | • 0        |

|   | 0.1          | logues             | <u> </u>                                                         | 75         |

|   |              | 6.1.1              | Abstract Generating Automatons and Soundness                     | 77         |

|   |              | 6.1.2              | The Refinement Algorithm                                         | 80         |

|   | 6.2          |                    | ation to Abstraction and Refinement Analogues                    | 82         |

|   | ~ · <b>-</b> |                    | Functions without Control Flow                                   | 82         |

|              |                                                             | 6.2.2   | Functions with Conditional Branches                       | . 84 |  |  |  |

|--------------|-------------------------------------------------------------|---------|-----------------------------------------------------------|------|--|--|--|

|              | 6.3                                                         | Implei  | mentation Specifics                                       | . 85 |  |  |  |

|              |                                                             | 6.3.1   | Resolution of Introduced Complications                    | . 86 |  |  |  |

|              | 6.4                                                         | Verific | eation of AVR Programs                                    | . 88 |  |  |  |

|              |                                                             | 6.4.1   | Description Details and Evaluation Setup                  | . 89 |  |  |  |

|              |                                                             | 6.4.2   | Toy Programs                                              | . 90 |  |  |  |

|              |                                                             | 6.4.3   | Factorial: Stack Overflow Avoidance                       | . 92 |  |  |  |

|              |                                                             | 6.4.4   | Digital Calibration: Finding a Bug in a Realistic Program | 93   |  |  |  |

|              |                                                             | 6.4.5   | Assessment of Capabilities and Possible Improvements      | 96   |  |  |  |

| 7            | Con                                                         | clusio  | n                                                         | 99   |  |  |  |

|              | 7.1                                                         | Summ    | nary                                                      | 99   |  |  |  |

|              | 7.2                                                         |         | ibutions of the Dissertation Thesis                       |      |  |  |  |

|              | 7.3                                                         |         | e Work                                                    |      |  |  |  |

| Bi           | ibliog                                                      | graphy  |                                                           | 103  |  |  |  |

| R            | eview                                                       | ved Pu  | ablications of the Author Relevant to the Thesis          | 113  |  |  |  |

| R            | Remaining Publications of the Author Relevant to the Thesis |         |                                                           |      |  |  |  |

| $\mathbf{R}$ | e <b>mai</b> i                                              | ning P  | Publications of the Author                                | 117  |  |  |  |

# **List of Figures**

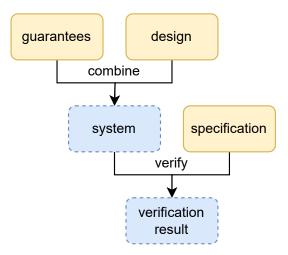

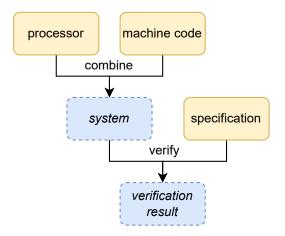

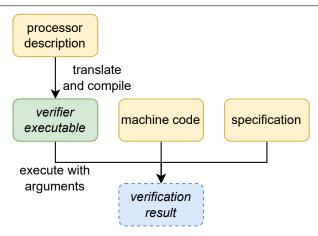

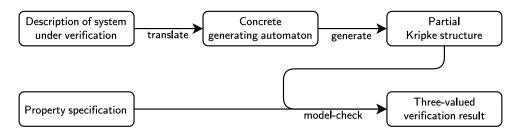

| 2.1 | Overview of formal verification of digital systems                            | 8  |

|-----|-------------------------------------------------------------------------------|----|

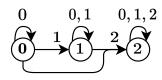

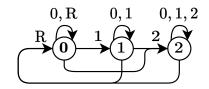

| 4.1 | Systems that compute the maximum running value of the input                   | 38 |

| 4.2 | Strategies for path prefix splitting                                          | 41 |

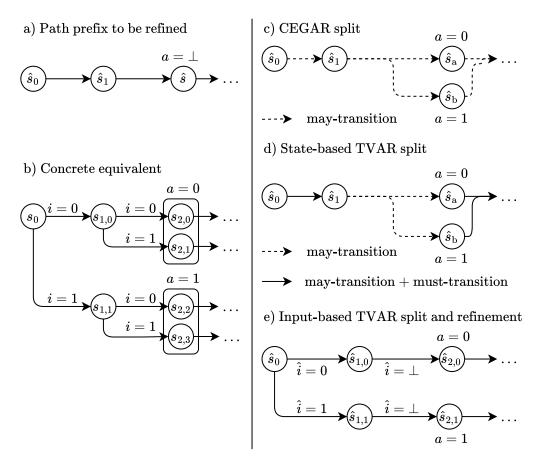

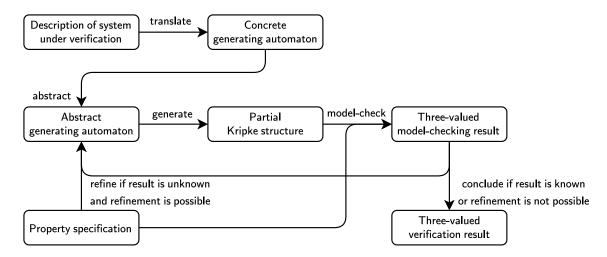

| 4.3 | Block overview of concrete verification                                       | 44 |

| 4.4 | Block overview of the proposed input-based Three-valued Abstraction Refine-   |    |

|     | ment framework                                                                | 45 |

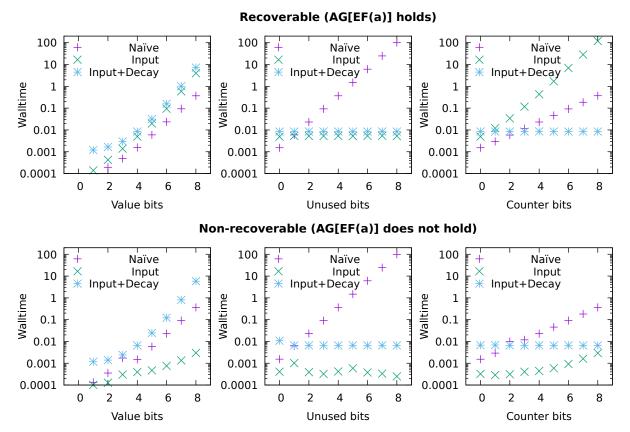

| 4.5 | Wall-time elapsed during verification of the recovery property                | 52 |

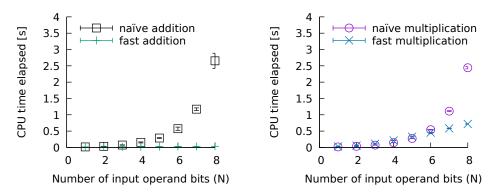

| 5.1 | Measured computation times for $10^6$ random abstract input combinations      | 73 |

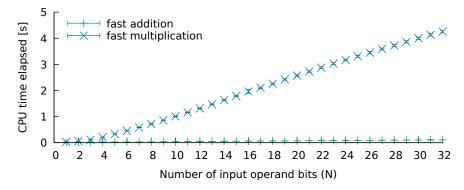

| 5.2 | Measured computation time for $10^6$ random abstract input combinations, fast |    |

|     | algorithms only                                                               | 73 |

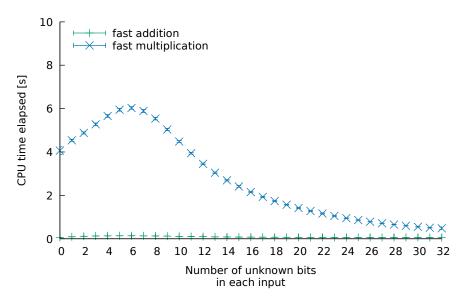

| 5.3 | Measured computation times for $10^6$ random abstract input combinations with |    |

|     | fixed $N=32$ , while the number of unknown bits in each input varies          | 74 |

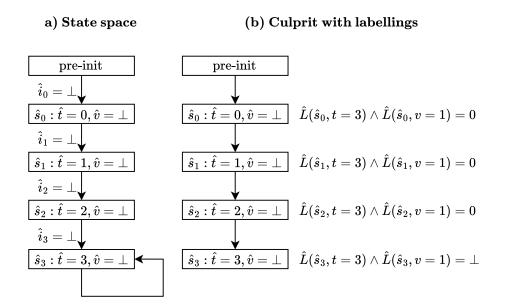

| 6.1 | An example of a lasso-shaped state space and the culprit                      | 81 |

| 6.2 | A function without control flow and its abstract and refinement analogues     | 83 |

| 6.3 | A function with branching and its abstract analogue                           | 84 |

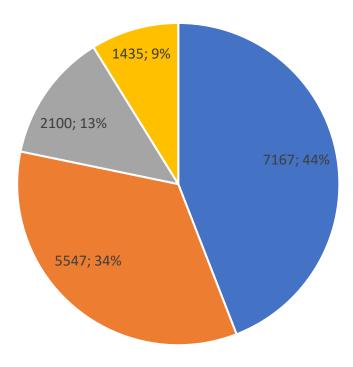

| 6.4 | Categories of lines of Rust code in machine-check                             | 87 |

| 6.5 | The factorial program                                                         | 92 |

| 6.6 | The simplified calibration program                                            | 94 |

# **List of Tables**

| 6.1 | Measurements of machine-code verification of toy programs using <b>machine-</b>  |           |

|-----|----------------------------------------------------------------------------------|-----------|

|     | check-avr                                                                        | 91        |

| 6.2 | Measurements of machine-code verification of the factorial program using machine | <b>e-</b> |

|     | check-avr.                                                                       | 93        |

| 6.3 | Measurements of machine-code verification of the calibration program using       |           |

|     | machine-check-avr                                                                | 95        |

# List of Algorithms

| 5.1 | Modular extreme-finding abstract algorithm blueprint |      |  |  |  |  |  | 62 |

|-----|------------------------------------------------------|------|--|--|--|--|--|----|

| 5.2 | Fast abstract multiplication algorithm               | <br> |  |  |  |  |  | 70 |

## **Abbreviations**

#### Commonly Used Abbreviations

**BDD** Binary Decision Diagram

**CEGAR** Counterexample-guided Abstraction Refinement

CTL Computation Tree LogicGA Generating Automaton

**GPIO** General-Purpose Input/Output

KS Kripke Structure

**KMTS** Kripke Modal Transition Structure

LTL Linear Time Logic PC Program Counter

**PKS** Partial Kripke Structure

SAT Boolean Satisfiability Problem

**SMT** SAT Modulo Theories

**SP** Stack Pointer

**SRAM** Static Random-Access Memory

TVAR Three-valued Abstraction Refinement

#### Less Common Mathematical Notation

Number 3 expressed in binary numeral system

Ox1F Number 31 expressed in hexadecimal numeral system

$\{0,1\}^n$  n-ary Cartesian power of set  $\{0,1\}$

$\stackrel{\text{def}}{=}$  Defined as

#### Three-valued Abstraction Notation

'0' Three-valued abstraction value corresponding to "definitely 0" '1' Three-valued abstraction value corresponding to "definitely 1"

'X' Three-valued abstraction value corresponding to "perhaps 0, perhaps 1"

"1X10" A tuple of three-valued abstraction values

#### Typesetting

italic A concept that is being introduced

bold A tool, an executable, a competition,

or a temporal logic operator represented by a letter

typewriter A code identifier or a Rust package

## Introduction

The presence of bugs in programs for computers and embedded systems may have severe consequences for safety, security, reliability, etc. Source-code-level and hardware-level verification has been explored in great detail, resulting in applicable tools for formal verification. Machine code level, especially important for embedded systems with wide use in safety-critical industries such as medical, automotive, and aeronautics, has not enjoyed the study and availability of formal verification tools on such a scale. Formal verification of machine-code systems is problematic due to a unique combination of challenges: large state spaces, the loss of high-level information about the programs, and the diversity of various processor architectures.

Previously, in my diploma thesis [A.4], I noted that there were no publicly available formal verification tools for machine-code systems, and created a tool based on previous research, using the ubiquitously used model checking with abstraction. However, it was not good enough for practical purposes due to the aforementioned challenges. In particular, abstraction refinement is typically used in state-of-the-art tools for formal verification of source-code and hardware systems to reduce the state space size, but adding it while allowing for diverse processor architectures was previously not reasonably possible.

I set out to overcome the challenges, at least partially, during my doctoral research. I devised three novel techniques, described them in publications and implemented them in my publicly available, free, and open-source formal verification tool **machine-check**<sup>1</sup>, a spiritual successor to my previous tool. In this thesis, I comprehensively present the background of my work, the devised techniques, as well as their experimental evaluation. Using my tool, I was able to verify that various specifications hold in bare-metal programs for the AVR ATmega328 microcontroller. The techniques enable verification in reasonable time and memory without problems of the previous tools, substantially improving the state of the art in formal verification of machine-code systems.

<sup>&</sup>lt;sup>1</sup>The latest release of **machine-check** is available at https://crates.io/crates/machine-check. The current release at the time of writing this thesis is available at https://crates.io/crates/machine-check/0.3.0.

#### 1.1 Contribution

I devised, described, and, where applicable, formally proved three novel techniques:

- Translation of simulable machine-code system descriptions. Previously, tools for formal verification of machine-code systems were largely tailored to a specific processor, and abstraction was managed manually, making the addition of new processors and architectures highly complicated and time-consuming. I devised a scheme where the processors are described in the programming language Rust and automatically translated to their verification analogues at compile time using meta-programming. I published an overview of the scheme [A.2].

- o Input-based three-valued abstraction refinement framework. The usual abstraction refinement scheme is Counterexample-guided Abstraction Refinement (CE-GAR), which cannot verify some system properties, importantly including whether the system can recover to a specified state from any state. Properties such as recovery can be verified using the stronger Three-valued Abstraction Refinement (TVAR), but the previous abstraction refinement frameworks based on TVAR were problematic. Therefore, I devised a novel framework based on TVAR that resolves the problems, and proved that it can be used for formal verification of arbitrary properties of propositional μ-calculus. A preprint of my work is available [A.3].

- Three-valued bit-vector arithmetic. When using abstraction, the abstract domains of system-state variables must be chosen, with a dramatic impact on verification speed and the ability to prove or disprove properties. In machine-code systems, it is typical that only one specific bit of an input port determines whether the property holds or not. This can be abstracted well by three-valued bit-vector abstraction, but it was previously not possible to quickly compute useful results of arithmetic operations using such abstraction. I devised a novel technique for computing useful results in polynomial time, with the best possible results for addition and multiplication computable in linear and quadratic time, respectively. I described, formally proved, and published the technique together with my supervisor [A.1].

I implemented the techniques in my free and open-source tool **machine-check**. It is able to verify properties of machine-code programs as well as any other systems that can be described as finite-state machines. The required time and memory are reasonable for simple programs, and the framework and its implementation are conducive to improvements in abstraction and refinement strategies, paving the way to full formal verification of security-and safety-critical systems, not just their hardware or source-code components.

While my research was focused on the machine-code level, the techniques are general and of interest in other fields of formal verification, especially of source-code and hardware systems. The input-based TVAR framework in particular is fully general and can be used to verify properties not verifiable by current state-of-the-art tools, further supporting the overarching goal of leveraging formal verification for greater security and safety.

## 1.2 Organisation of This Thesis

The dissertation thesis is organised into chapters as follows:

- 1. **Introduction**: Describes the contribution of my research.

- 2. Background and State of the Art: Introduces the reader to the necessary theoretical background and surveys the current state of the art.

- 3. Translation of Simulable Machine-Code System Descriptions: Describes the technique of translation of simulable descriptions used in my tool machine-check. Contains previously published material [A.2] with further additions.

- 4. Input-based Three-valued Abstraction Refinement Framework: Describes the Three-valued Abstraction Refinement framework I proposed and implemented, elegant yet more powerful than the commonly used Counterexample-guided Abstraction Refinement frameworks. It is proven that its important characteristics, which make it suitable for formal verification, depend only on fairly simple requirements. Contains material available as a preprint [A.3].

- 5. Abstract Three-valued Bit-vector Arithmetic: Describes a three-valued abstraction domain that is useful for digital (especially machine-code) systems, and presents fast algorithms for addition and multiplication within the domain, with proofs that they produce the best possible results. Contains previously published material [A.1].

- 6. Created Machine-Code Formal Verification Tool machine-check: Describes the combination of the techniques from Chapter 3, 4, and 5 and further considerations for implementation of the formal verification tool that I created during work on this thesis. Discusses an experimental evaluation of the tool on machine-code systems.

- 7. **Conclusion**: Summarises the results of my doctoral research, suggests possible topics of further research, and concludes the dissertation thesis.

## Background and State of the Art

The rise of digital electronic systems to ubiquity in our lives has brought a multitude of challenges. Computing devices are no longer restricted to mainframes and personal computers but are present in all kinds of aspects of our lives including medical devices, home appliances, or toys. Most of us carry a mobile phone, and we rely on transport by cars, trains, ships, and aeroplanes, all of them increasingly dependent on electronic control. All aspects of our lives, including our security and safety, are reliant on the systems behaving correctly. Nevertheless, just during the last two months of writing this thesis,

- the outage caused by the CrowdStrike software glitch paralysed the global economy and resulted in losses estimated in billions of dollars [1],

- the leading processor manufacturer Intel has responded to the instability of its 13th and 14th generation processors, releasing a processor microcode update which is supposed to fix incorrect voltage requests that result in processor degradation [2],

- a vulnerability was found in AMD processors including the current generation [3], undetected for almost 20 years, allowing the planting of nearly undetectable malware once kernel-level access is obtained [4].

While informal testing of systems can reveal some bugs, formal verification can definitely prove or disprove that a given specification holds in a given system, preventing bugs that arise from unconsidered corner cases. Unfortunately, it is much more problematic to formally verify systems than to create them. Continual advances in formal verification are necessary to prevent the consequences of bugs such as drastic monetary loss, data theft, loss of privacy, and even human injury.

Formal verification is a wide field of computer science which overlaps with other fields such as graph theory, automata theory, combinatorial optimisation, static program analysis, and testing. As such, in this chapter, I discuss only topics of direct relevance to the subject of this dissertation thesis. Related work that is only relevant to a single chapter will be discussed in the respective chapter.

In this thesis, I focus on formal verification of machine-code programs against specifications. The main processors under consideration are simple embedded microcontrollers, the programs are bare-metal, without any operating system layer. Machine-code verification is especially sensible in this scenario, as source-code verification may not be able to verify properties such as correct initialisation and usage of peripherals. Some parts of the program may also be hand-written in assembly language to achieve maximum performance, precluding source code verification. Lastly, the compiler may contain bugs, resulting in possible issues that are undetectable using source-level verification. The aforementioned concerns make machine-code verification an important and irreplaceable avenue of approach.

For a comprehensive understanding of the task, there are three major areas to explore:

- The digital systems under verification, their levels (hardware, machine code, source code), and commonalities shared by systems of all levels.

- The specifications for which we are trying to decide whether they hold in a given system.

- The techniques for formal verification.

These areas are interrelated: the digital systems are usually formalised as automata, and so the typical specification formalisms are based on states and paths through the automata. The verification techniques are based on the formalised systems and specifications. Adherence of finite-state systems to common temporal specifications can be verified in time and space linear to the state space size, with further improvements possible through the use of advanced techniques.

In this chapter, I will explore systems, specifications, and verification techniques. After that, I will focus on formal verification using model checking with abstraction refinement. Finally, I will examine the state of the art in formal verification of digital systems, noting the lack of usable tools for verification of machine-code systems.

## 2.1 Digital Systems

As proven by Shannon [5], systems comprised of switching circuits can be used to solve arbitrary problems specified in Boolean algebra by the construction of logic gates. The rise of transistor technology, especially Complementary Metal-Oxide-Semiconductor (CMOS) technology, has allowed us to construct systems with computation capabilities far overshadowing other kinds of systems. The systems are inherently parallel in nature, each logic gate only dependent on the ones producing its inputs.

While electronic hardware systems can be designed to perform fixed computations with great performance and little power consumption, the design and initial manufacturing expenses for such devices are prohibitive for most applications. As such, programmable devices are now commonly used as well. It is possible to group them into two categories, notwithstanding System on a Chip (SoC) combinations:

- Programmable Logic Devices (PLDs) are devices in which reconfigurable digital circuits can be configured to perform specified computations using basic elements such as logic gates and flip-flops, similarly to building the digital circuits themselves. The most complex of these devices are Field-Programmable Gate Arrays (FPGAs).

- Processors are devices that manipulate their state according to machine-code-program instructions. This typically results in less parallelism, with sequential program flow in each processor core. The programmer typically writes a source-code program in a programming language such as C, which is then compiled to machine code that is executed by the processor.

Let us suppose that we want to create a digital system. We are only responsible for designing a small part of the overall system, building on top of underlying components. For example, in a machine-code system, we design the machine code that will be executed on the selected processor and rely on the guarantees by the processor manufacturer that it will perform as described in its accompanying documentation. We devise the machine code based on these guarantees (not the physical device itself): without knowing anything about the processor behaviour, the machine code is just a meaningless sequence of bits.

In this thesis, I will use the noun *design* to refer to the part of the system that is under our control, and the noun *guarantees* to refer to the guarantees about the behaviour of the underlying parts of the system outside of our control. The design and guarantees combine to form the *system*. For verification purposes, the whole system must be considered, as visualised in the block overview in Figure 2.1.

The digital system will ultimately be backed by a physical device that behaves according to the physical reality. As such, there must be fundamental guarantees that the device behaves digitally. During verification, we assume that all guarantees hold, as we are only concerned with detecting problems where we are at fault, not problems arising due to the given guarantees not holding in the actual device.

In case the design is described in a language with formal syntax and semantics, basic guarantees are defined by the semantics of the formal language. However, there might be additional guarantees.

Example 2.1.1. Let us consider that we are writing a source-code program in the C language, and our compiler adheres to the C99 standard [6]. The language semantics defined in the standard give us basic guarantees about how the program will behave once compiled and executed, barring e.g. bugs in our compiler or a defective processor we will be compiling or executing the program on. We can also use libraries, with which we communicate using Application Programming Interfaces (APIs), with additional guarantees of their behaviour. When verifying our program, we take the source code we have written and the guarantees (language semantics and API guarantees) into account.

Figure 2.1: A high-level overview of formal verification of digital systems. The solid yellow cells represent verification inputs, while the dashed blue cells represent an automated combination or result. The guarantees and the design are combined together to form the system under verification. It is then determined if the specification holds.

#### 2.1.1 Digital System Levels

In the vast majority of cases, a digital system can be placed into one of three separate levels:

- o A hardware system is a combination of the digital design described in a design language, the basic guarantees provided by the design language, and possibly additional guarantees provided by e.g. Intellectual Property (IP) blocks. The design language is typically a Hardware Description Language (HDL) such as VHDL or Verilog. For formal verification, the systems are typically first translated to the AIGER format [7, 8] that describes the whole system as a sequence of gates or the Btor2 format [9] that describes the systems by bit-vectors and bit-vector arrays, preserving operations such as addition or multiplication instead of translating them to logic gate combinations. After translation, the guarantees are formed by the AIGER/Btor2 format semantics.

- A machine-code system is a combination of the design in the form of machine code, the basic executing processor guarantees, and possibly additional guarantees for e.g. circuits connected to the processor pins. For bare-metal use, the machine code is typically in the Intel HEX format [10]. For usage with operating systems, the machine code is typically bundled with some additional information, e.g. the Executable and Linkable Format (ELF) for Unix-like operating systems and the Portable Executable (PE) format for the Windows operating system. Unfortunately, the processor guarantees are usually not available as a formal specification, the informal documentation being provided in the form of the processor datasheet, the user manual, the instruction set architecture manual, etc.

A source-code system is a combination of the design in the form of source code

in a programming language, the basic guarantees provided by the semantics of the

programming language, and possibly additional guarantees provided by e.g. the APIs

of the used libraries. The programming languages can be standardised, as in the case

of the ubiquitous C99 standard [6], but their more difficult semantics are typically

described informally.

Some digital systems cannot be placed into a single level, such as source-code programs with inline assembly which combine source-code and machine-code characteristics, but I will not discuss them in this thesis for the sake of conciseness. Between the three levels, there are two special system types that seemingly mix the characteristics but tend to be closer to one level:

- A bytecode system is a combination of the design in the form of bytecode for a Virtual Machine (VM), basic guarantees provided by the bytecode specification, and possibly additional guarantees. The bytecode serves as an intermediate stage before interpretation or compilation on the target machine. The typical program bytecode is for the Java Virtual Machine (JVM). LLVM IR (Intermediate Representation) is used as an intermediate compilation stage for the LLVM compiler suite [11]. While the bytecode is a sequence of bits similar to machine code, the system as a whole is much more similar to a source-code system, with device-agnostic guarantees. Bytecode is sometimes used for verification in place of source code due to similar expressivity but simpler constructs.

- A microcode system is a combination of the design in the form of microcode and the underlying hardware guarantees, implementing a processor that is supposed to execute machine code with the guarantees given by the processor manufacturer. Structurally, the microcode system can be considered a machine-code system which serves to provide a Virtual Machine for the higher-level machine code.

During the discussion of the state of the art in Section 2.6, I will discuss the bytecode and microcode systems grouped with source-code and machine-code systems, respectively.

**Example 2.1.2.** Throughout this thesis, I will focus on AVR ATmega328P, a mid-line 8-bit microcontroller which is famously used in the Arduino Uno development boards. The microcontroller integrates an 8-bit AVR processor core with 32 working registers and additional Input/Output (I/O) registers together with 2048 bytes of Static Random Access Memory (SRAM) that is used as data memory and 1024 bytes of Electrically Erasable Programmable Read-Only Memory (EEPROM) that is used as program memory [12].

The hardware level of the microcontroller is known to the AVR processor manufacturer Microchip (which has acquired the former manufacturer Atmel), but not to the general public. The programs are usually written either in the C language (source code level) and compiled to machine code or in the AVR assembly language that corresponds to the machine-code instructions directly and is assembled to machine code. The instruction set is publicly available [13].

Note 2.1.3. Digital systems can be described using many specific languages, such as modelling languages (UML, SysML), simulation-oriented languages (Matlab-Simulink etc.), or verification-specific languages [14]. However, these languages usually present some general overview of the system, not a fully specified system that can be used in the real world. I will not discuss the specific languages further and will show in Chapter 3 that it is possible to describe digital systems using a general-purpose programming language and still retain the ability to use advanced verification techniques.

#### 2.1.2 Digital System Commonalities

The transition from hardware up to source code is essentially a transition from physical systems to systems that correspond to human (predominantly sequential) reasoning. There are important commonalities between the systems, combining building blocks that are physically efficient and those that are conducive to human reasoning. These commonalities can be found by examining HDL languages, common processor architectures, and imperative programming languages:

- Binary digits. While other bases such as ternary and decimal have enjoyed some popularity in the past, the current digital systems are ubiquitously binary.

- Finite-width bit-vector variables. Unlike mathematical variables, the variables refer to some over-writable physical memory location. Only finite-width bit-vectors are physically implementable in the binary digital logic. They are used as basic building blocks for describing real-world digital systems.

- Arrays and array indexing. Bit-vector arrays are ubiquitously used. In machine-code systems, only a few arrays are exposed through the machine-code instructions, typically including working registers and either the main memory (von Neumann architecture) or the program memory and the data memory (Harvard architecture). In imperative programming languages, only the main memory is exposed, and variables used to index into it are called *pointers* (typically treated differently from other variables to prevent bugs).

- Fixed-point bit-vector operations. There are five basic types of almost universally available bit-vector operations: bitwise operations, bit-shift operations, bit length manipulation operations, arithmetic operations, and relational operations. Some operations (such as bit extension or division) are dependent on the interpretation of the bit-vector, which is today almost universally treated as either unsigned or signed in two's complement. The interpretation is chosen either by the variable type (e.g. in typical imperative programming languages or VHDL numeric\_std) or by a special operation choice (e.g. the processor instruction type).

While bit-vectors do not perfectly correspond to the mathematical notions of numbers, arithmetic operations can be performed using them if the distinctions are observed (e.g. sizing the variables to prevent overflows). While the arithmetic and relational operations

are provided due to the need to perform arithmetic and comparisons in number-based algorithms, the bitwise and bit-shift operations are provided because they are efficiently implementable. The combination allows for a number of "hacks", such as fast multiplication and division by powers of 2 using bit-shifting [15].

Note 2.1.4. Floating-point operations are outside of the scope of this thesis. Common processors and language implementations typically follow the IEEE 754 standard to a certain extent. Floating-point variables can be described as bit-vectors and the operations can be converted into bit-vector operations (soft floating point).

**Example 2.1.5.** In ATmega328P, the working registers, the data memory, and the program memory are the most important bit-vector arrays. I/O addresses can correspond to I/O registers or have special behaviour (e.g. reading digital values of microcontroller pins). Typical instructions perform indexing (e.g. of two registers) and perform some fixed-point operations using the indexed locations (e.g. adding the two registers and writing the result into one of them, writing status flags afterwards). The arithmetic operations mostly operate on 8-bit bit-vectors. Floating-point operations are not supported and must be emulated with soft floating point if necessary. The instructions correspond closely to C operations on 8-bit integers and are efficiently implemented in hardware, with most instructions executing in one clock cycle.

The commonalities can be used to describe the system at another system level or even automatically translate between the levels, adjusting the design to the new guarantees so that the overall system behaviour remains the same. In my approach, the machine-code system guarantees (mainly describing the processor behaviour) are described at the source-code level in the Rust programming language, leveraging its advantages. This will be elaborated upon in Chapter 3.

#### 2.1.3 Formalisation as Moore Machines

Digital systems can be formalised as general automata with outputs. In practice, constructable systems are always finite, and can be formalised by deterministic Moore or Mealy Finite State Machines (FSMs): the system deterministically changes its state based on the values of its inputs and its behaviour is reflected in its outputs. I will discuss the Moore machine formalism as it is simpler.

**Definition 2.1.6.** A Moore machine M is a tuple  $M = (S, s_0, \Sigma, \Omega, \delta, \lambda)$  where

- $\circ$  S is a finite set of states,

- $\circ$   $s_0 \in S$  is the initial state,

- $\circ \Sigma$  is the input alphabet, a finite set,

- $\circ \Omega$  is the output alphabet, a finite set,

- $\circ \ \delta: S \times \Sigma \to S$  is the state transition function,

- $\circ \lambda: S \to \Omega$  is the output function.

The behaviour of the system is determined by the outputs of the successive states, starting in the initial state and applying the state transition function with the selected inputs. Dropping the requirements of finite S,  $\Sigma$ , and  $\Omega$ , the resulting formalisation allows for non-constructable systems as well, such as source-code programs with variables that are unrestricted natural numbers.

The formalisation captures the system behaviour but not the practical considerations. Most notably, it is typically only necessary to consider the states and transitions reachable from the initial state, as the others are irrelevant to system behaviour. The commonalities from Subsection 2.1.2 are hidden in the definitions of  $S, \Sigma, \Omega, \delta$ , and  $\lambda$ , despite having an important practical role in the speed of simulation and verification of the system.

## 2.2 Property Specifications

Formalising digital systems as Moore machines allows for proving their predicate calculus properties. However, automatically formally verifying predicate calculus properties w.r.t. the machines is problematic for two reasons:

- Proving in reasonable time and memory. Trivially, proving or disproving that finite specifications (of finite length and with finite quantified variables) hold in finite systems can be accomplished in finite time and with finite memory using brute force. However, the amount of reachable states tends to grow exponentially to the input size, and verifying the specification can introduce further slowdowns. Furthermore, checking the properties of infinite paths is even more problematic.

- Specifications difficult to express in predicate calculus. In the specifications, we typically are concerned about properties of system states and paths through the system that might not be intuitive to express in predicate calculus.

While the full predicate calculus is too general, properties that only consider a single state of the system are too limited. *Temporal logics*, which describe the behaviour as paths through the state space are taken, are a good compromise and have become the most commonly used specification formalisms in formal verification. A temporal logic forms a useful, well-defined set of formulas with respect to the system under verification, referring not only to individual states but also to paths, which are typically infinite. Formulas of common temporal logics can be directly translated to predicate logic formulas.

The most important temporal logics in formal verification are Computation Tree Logic (CTL), Linear Time Logic (LTL), and CTL\*, of which CTL and LTL are subsets. For conciseness, I will define CTL\* first and then introduce CTL and LTL using it.

**Definition 2.2.1.** A CTL\* property is a logical formula consisting of either an atomic proposition or a logical operator combining other CTL\* properties. There are three kinds of such operators in CTL\* [16, p. 7-10]:

- Propositional logic operators. Typically, these are  $\neg \phi$ ,  $\phi \land \psi$ ,  $\phi \lor \psi$ ,  $\phi \Rightarrow \psi$ ,  $\phi \Leftrightarrow \psi$ .

- **Temporal operators.** These operators encode the desired behaviour on an infinite path through the system. There are five such operators:

- $-\mathbf{X}\phi$  (next). The property  $\phi$  has to hold at the next state of the path.

- $\mathbf{G}\phi$  (globally). The property  $\phi$  has to hold in every state on the path.

- $\mathbf{F}\phi$  (finally). The property  $\phi$  has to hold in some state on the path.

- $[\phi \mathbf{U}\psi]$  (until). The property  $\phi$  has to hold until  $\psi$  holds (not including the first state where  $\psi$  holds), and  $\psi$  must hold in some state on the path.

- $[\phi \mathbf{R} \psi]$  (release)<sup>1</sup>. The property  $\psi$  has to hold before and during the first state in which  $\phi$  holds, but  $\phi$  does not have to ever hold (in which case,  $\psi$  must hold forever). In other words,  $\phi$  releases  $\psi$ .

- Path quantifiers. These operators encode the quantification of paths from a given state.

- $\mathbf{A}\phi$  (along all paths, inevitably). The property  $\phi$  must be true in all paths from the given state.

- $\mathbf{E}\phi$  (there exists a path, possibly). The property  $\phi$  must be true in at least one path from the given state.

For evaluation, the CTL\* formula is implicitly enclosed by an along-all-paths quantifier if necessary (i.e. there exists a temporal operator not enclosed by a path quantifier), similarly to implicit universal quantification of free variables in predicate calculus. The resultant formula can be evaluated on arbitrary states of the system under verification. When a system with multiple initial states is considered, the CTL\* property must hold in all initial states to hold in the system itself.

**Example 2.2.2.** Some of the more notable CTL\* formula schemes are:

- $\circ$  Safety. AG[ $\phi$ ], i.e. on all paths,  $\phi$  holds forever.

- $\circ$  **Reachability.**  $AF[\phi]$ , i.e. on all paths, a state where  $\phi$  holds is reached.

<sup>&</sup>lt;sup>1</sup>In some literature, the release operator is not included in CTL\* and its subsets, simplifying the definition at the expense of losing operator duality. Alternatively,  $[\phi \mathbf{R} \psi]$  can be thought of as an alias for  $\neg [(\neg \phi) \mathbf{U}(\neg \psi)]$ .

- Recovery.  $AG[EF[\phi]]$ , i.e. from every reachable state, there exists a path to a state where  $\phi$  holds in the future. In other words, we can always somehow coerce the system to reach a state where  $\phi$  holds.

- Invariant lock.  $AG[\phi \Rightarrow AG[\phi]]$ , i.e. once  $\phi$  holds, it holds forever.

- Action-reaction.  $AG[\phi \Rightarrow AF[\psi]]$ , i.e. once  $\phi$  holds,  $\psi$  must hold in that state or some successive state.

As stated previously, the two most ubiquitous subsets of CTL\* are CTL and LTL:

- In CTL, the path quantifiers and temporal operators can only come in pairs in that order, e.g.  $\mathbf{AG}\phi$  or  $\mathbf{E}[\phi\mathbf{U}\psi]$ . In essence, CTL allows posing statements about the current state and states following it, but not arbitrary paths.

- In LTL, no path quantifiers are permitted in the formula, the only one being the implicit along-all-paths quantifier. For example, the LTL formula  $\mathbf{FG}\phi$  could be more clearly expressed in CTL\* as  $\mathbf{AFG}\phi$  [16, p. 9]. In essence, LTL describes each path through the state space separately, and the result is whether this description holds for all paths.

Each CTL\* property can be translated into an equivalent formula of the (stronger) predicate μ-calculus [17, p. 907]. While the proofs in Chapter 4 are general enough for arbitrary μ-calculus properties, I will not discuss μ-calculus in detail as it is less understandable than classic temporal logics and it is not easy to find interesting properties expressible in it but not in CTL\*.

## 2.3 Formal Verification Using Model Checking

Formal verification of systems against specifications can be accomplished in a multitude of ways. The most basic one is through manual proofs. However, that approach is only realistic for very simple systems. It is possible to construct automated proofs, but as the systems become complicated, devising the choices to make in the proofs becomes problematic. Fortunately, for finite-state state-transition systems, it is possible to use the model-checking approach to prove or disprove the properties completely automatically. In model-checking, the state space of the finite-state system is constructed and the properties are verified against the state space instead of the original system [16, p. 1-3]. This allows for completely automatic verification of the system in finite time and memory.

Unfortunately, while model checking seems excellent in theory, there are two main practical challenges encountered [16, p. 3-4]:

• Scalability. While the time and memory needed for model-checking is finite, in practice, it is infeasible to model-check all but the simplest systems without using advanced techniques. This is mainly due to the exponential explosion during the

construction of the reachable state space (also termed state space explosion): in each state, N input bits result in up to  $2^N$  successor states being generated.

• Modelling. The classic model-checking formalisms essentially verify whether temporal logic specifications hold in finite-state machines. The modelling challenge is to fully capture many possible systems of interest, including unbounded systems and differently descriptive specifications (i.e. real-time logics).

The scalability and modelling challenges are subjects of ample research [16]. Both are major challenges to machine-code verification, although the modelling challenge is present mainly in the practical rather than in the theoretical sense, as the classic model-checking formalisms capture the nature of digital systems well.

#### 2.3.1 Classic Model-Checking Formalisms

I will now introduce the classic formalisms for formal verification using model checking [16]. The name model checking is taken from mathematical logic: we are checking whether the formalism of the system, a Kripke structure K, is a model of the specification  $\phi$ , i.e. whether all sentences in  $\phi$  are true with respect to K. The fact that K is a model of  $\phi$  is usually written as  $K \models \phi$ , and that fact that it is not is written as  $K \not\models \phi$ . The model-checking tool, given K and  $\phi$ , ideally outputs either  $K \models \phi$  or  $K \not\models \phi$  (and perhaps some additional information such as the reasons for that result). In practice, it also may not give us any answer at all, such as when verification time or memory is exceeded.

**Definition 2.3.1.** A Kripke structure over a set  $\mathbb{A}$  of atomic propositions is defined as a tuple  $K = (S, S_0, R, L)$  where

- $\circ$  S is the set of states,

- $\circ$   $S_0 \subseteq S$  is the set of initial states,

- $\circ R \subseteq S \times S$  is a transition relation,

- $\circ L: S \times \mathbb{A} \to \{0,1\}$  is a labelling function, which determines whether each atomic proposition holds in a state or does not.

Note 2.3.2. I use the Kripke structure definition with initial states throughout this thesis for correspondence with real-life digital systems. Some definitions omit the initial states. I use a characteristic labelling function instead of the more common definition  $L: S \to 2^{\mathbb{A}}$  for easier formalisation of abstraction in Section 2.5.

The Moore machines from Section 2.1.3 can be easily turned into Kripke structures by replacing the output function with the labelling function (which may expose the internal state of the machine as well as the outputs), and turning the state transition function into a relation by considering all input possibilities. The major insight here is that the actual input values are unnecessary for computing the verification result. However, as discussed

later in Chapter 4, the inputs become relevant again when we are trying to determine what caused the result.

In classic model checking, the Kripke structure is checked against a CTL, LTL, or CTL\* property. Although these temporal logics work with infinite paths, there are algorithms that can verify their properties in a reasonable time:

- $\circ$  CTL. Running time depends linearly both on the size of K and the length of the CTL formula [16, p. 11].

- $\circ$  LTL. Running time depends linearly on the size of K and exponentially on the length of the LTL formula [16, p. 13].

- $\circ$  CTL\*. The algorithms for CTL and LTL can be simply combined [18, p. 69], resulting in running time depending linearly on the size of K and exponentially on the length of the CTL\* formula, the same as for LTL.

As the size of K is the major limiting factor, the ability to verify in time linear to it is crucial, explaining the popularity of CTL, LTL, and CTL\*. The state space explosion becomes the main problem.

**Example 2.3.3.** Let us consider formal verification of ATmega328P using naïve model checking. The I/O registers are reset during the device reset [12, p. 56], but the 32 working registers and 2048 SRAM bytes are not and may contain any value. The number of possibilities after reset is  $2^{2048+32} = 2^{2080}$ , which results in infeasibly many initial states. Even ignoring the initial possibilities does not save us. The General Purpose Input/Output peripheral allows reading of up to 8 binary pin values during single instruction execution. Reading four times in succession to different working registers produces  $(2^8)^4 = 2^{32}$  combinations. Clearly, naïve model checking is not suitable for machine-code verification.

## 2.4 Advanced Techniques for Model Checking

As the state space explosion precludes verification of complex systems, advanced techniques have been devised to verify the system without constructing and model-checking the whole Kripke structure. Such techniques can be roughly classified in three groups [16, p. 15-18]:

• Abstraction is an approach where, instead of model-checking the original Kripke structure K, an abstract structure  $\hat{K}$  with less information is model-checked. The result is either the same as for the original structure or is unknown due to the lack of information. As an unknown result is not useful, abstraction refinement can be used to keep adding information to  $\hat{K}$  where it is necessary for verification until a definite result of model-checking is obtained.

- Symbolic methods avoid construction of the Kripke structure by using symbolic logic expressions to represent states and/or transitions, essentially compressing the state space by using a more compact representation. There are two main symbolic method subgroups:

- Model checking with Binary Decision Diagrams (BDDs). Useful especially for low-level hardware circuits described by Boolean expressions where they can dramatically reduce state space size while retaining the verification complexity, but problematic to use with arithmetic expressions due to the reintroduction of exponential explosion.

- Model checking based on solving the Boolean satisfiability problem (SAT) and its extensions. The system and the specification are encoded into SAT formulas that are solved by general SAT solvers. This approach allows the separation of describing the systems from the actual verification, which is reduced to a combinatorial problem. LTL or ACTL\* formulas can be verified by SAT solvers². For CTL and its supersets, the stronger Quantified Boolean Formula (QBF) solvers are necessary.

- Structural methods exploit the structure of the code that defines the system. The structural methods are usually associated with parallel systems or complex reasoning, using symmetries, partial orders, or other higher-level information to avoid storing the whole Kripke structure.

In practice, the groups of approaches tend to be combined. In particular, symbolic methods and abstraction are very conducive to combination since they are cleanly separated: the symbolic methods are applied once the system is abstracted. In fact, the widely-used Counterexample-Guided Abstraction Refinement (CEGAR) methodology was originally described as used with BDDs [19] and later extended for use with SAT solvers [20]. The SAT solvers themselves have evolved to Satisfiability Modulo Theories (SMT) solvers, which support solving formulas with e.g. bit-vector or mathematical integer variables in addition to Boolean variables.

For my core use case of machine-code verification, the use of abstraction is key to reasonable state space sizes. Symbolic methods can be used with abstraction, and they are well-researched [21, 22], but their use is mostly an implementation decision rather than a fundamental concept in a verification tool. I did not feel the need to use structural methods at this point as they are most useful when some kind of parallelism is introduced, and non-parallel machine-code programs are problematic enough as-is. As such, I have focused on abstraction in my work, and will not discuss the other groups of techniques further except where used in state-of-the-art tools discussed in Section 2.6.

<sup>&</sup>lt;sup>2</sup>For systems with left-total transition relations, as later noted in Section 2.5.1.

## 2.5 Abstraction and Abstraction Refinement

The ideal process of model-checking can be represented as a function  $P_{\phi}: \mathbb{K} \to \{0,1\}$  where  $\mathbb{K}$  is the set of all Kripke structures containing the atomic propositions present in the specification  $\phi$ . For every  $K \in \mathbb{K}$ ,  $P_{\phi}(K) = 0$  means that the model-checker determined  $K \not\models \phi$ , and  $P_{\phi}(K) = 1$  means it determined  $K \models \phi$ . We can extend the process to model-checking Kripke-like structures that can lack some of the original information, representing the incomplete model-checking process by  $\hat{P}_{\phi}: \hat{\mathbb{K}} \to \{0,1,\bot\}$ , where the results 0,1 behave the same as previously and  $\bot$  (unknown) means nothing was proven or disproven due to the lack of information<sup>3</sup>. The three distinct valuations 0, 1,  $\bot$  give rise to three-valued logic, which will be discussed in more detail later in Chapters 4 and 5.

Abstraction in model checking consists of devising an incomplete structure  $\hat{K}$  for verification and verifying properties of K using it. The abstraction should be sound, never producing wrong results:

$$\hat{P}_{\phi}(\hat{K}) \neq \perp \Rightarrow \hat{P}_{\phi}(\hat{K}) = P_{\phi}(K). \tag{2.1}$$

While it may be infeasible to compute  $P_{\phi}(K)$  in practice, devising  $\hat{K}$  and computing  $\hat{P}_{\phi}(\hat{K})$  can be easier as  $\hat{K}$  can contain less information and have fewer reachable states. The obvious problem is that if  $\hat{P}_{\phi}(\hat{K}) = \bot$ , we have not learned anything useful about K, only that  $\hat{K}$  is not a good enough abstraction for our purposes. This problem is resolved by abstraction refinement, where, after computing  $\hat{P}_{\phi}(\hat{K}) = \bot$ , we refine  $\hat{K}$  to contain more information, and continue until  $\hat{P}_{\phi}(\hat{K}) \neq \bot$ . This refinement loop forms the core of abstraction refinement frameworks, which we design to be sound and, optionally, complete, always verifying that the specification either holds or does not in finite time and memory for finite systems and specifications.

Example 2.5.1. Continuing in the example of verification of machine-code programs for AVR ATmega328P, we can represent each bit in a bit-vector by one of three values, '0' (definitely zero), '1' (definitely one), or 'X' (unknown — possibly zero, possibly one), forming three-valued bit-vector abstraction (discussed further in Chapter 5). Representing each uninitialised or input bit by 'X', we can start with a single abstract state that has all working registers and SRAM locations unknown, and representing all step inputs as unknown as well, produce a single abstract state in each processor step, ending up with a lasso-shaped state space. Unfortunately, as the step function is required to preserve soundness, the result of verifying properties that are dependent on inputs will be unknown, rendering the abstraction fairly useless. It is necessary to choose the abstract bits that will be turned to '0' and '1' possibilities, increasing the amount of information at the cost of increased state space size. Using abstraction refinement, we can choose the bits of interest deductively, without any outside help.

<sup>&</sup>lt;sup>3</sup>Not being to able to prove or disprove due to the lack of information in  $\hat{K}$  is different than not being able to prove due to e.g. the model-checker being terminated due to exceeding time or memory. The former gives us useful information about  $\hat{K}$ , while the latter gives us nothing at all, and is thus not formally considered.

#### 2.5.1 Methodologies

Now that the basic notions are in place, we can discuss the abstraction refinement methodologies. While Chapter 4 contains a more comprehensive and formal description of common abstraction frameworks based on the methodologies, I will give a basic overview based on Dams and Grumberg [23] here.

First, I will consider that the commonly used existential abstraction is used, where the abstract states of  $\hat{K}$  are related to the concrete states of K by a concretization function  $\gamma: \hat{S} \to 2^S$ . In essence, an abstract state represents that the concrete system might be in any of the concrete states given by the concretization function. For conciseness, I will write that the abstract state covers a concrete state in if it contains it in its concretization. Similarly, I will write that a path of abstract states covers a path of concrete states exactly if, in each position, the abstract state covers the concrete one.

Counterexample-guided Abstraction Refinement (CEGAR). The introduced abstract structure  $\hat{K}$  is a Kripke structure but has a very different meaning compared to K. The states of  $\hat{K}$  are abstract states. The transitions present in the transition relation  $\hat{R}$  of  $\hat{K}$  give no useful information as they may or may not correspond to concrete transitions between the concrete states covered by the endpoints. However, it is required that the transitions in the complement of  $\hat{R}$  do not correspond to any such concrete transitions, i.e.

$$\forall (\hat{s}_{\text{head}}, \hat{s}_{\text{tail}}) \in (\hat{S} \times \hat{S}) \setminus \hat{R} . \forall (s_{\text{head}}, s_{\text{tail}}) \in \gamma(\hat{s}_{\text{head}}) \times \gamma(\hat{s}_{\text{tail}}) . (s_{\text{head}}, s_{\text{tail}}) \notin R.$$

(2.2)

Additionally requiring covering each state in  $S_0$  by at least one state in  $\hat{S}_0$ , the set of paths in K is *overapproximated* by the set of paths in  $\hat{K}$ . Each path in K is covered by some path in  $\hat{K}$  but a path in  $\hat{K}$  can cover zero paths in K.

Assuming that R is left-total<sup>4</sup>, the temporal properties expressible in LTL or the universal fragments of CTL, CTL\*, and propositional  $\mu$ -calculus (the universal fragment essentially precludes existential quantifiers when the property is expressed in negation normal form) depend only on the set of paths, so we can use  $\hat{K} \models \phi$  to conclude  $K \models \phi$ . However, it is not possible to use  $\hat{K} \not\models \phi$  to conclude  $K \not\models \phi$ , as the counterexample path may not be contained in the set of paths in K (it may be *spurious*). However, we can overcome the problem by using the following refinement loop:

- 1. Model-check  $\hat{K}$  instead of K. If  $\hat{K} \models \phi$ , conclude that  $K \models \phi$ : as the aforementioned properties are violated by paths and  $\hat{K}$  covers all paths in K, the property must hold in K when it does in  $\hat{K}$ .

- 2. We know that  $\hat{K} \not\models \phi$ . Obtain a path that violates the property in  $\hat{K}$  (the *counterexample*) and validate if it violates the property in K as well. If it violates the property in K, conclude  $K \not\models \phi$ , providing the counterexample.

$<sup>^4</sup>$ If the transition relation in K is not left-total, there are some implicit existential characteristics in the universal fragment of CTL\* and some of its subsets [23, p. 392-393]. Fortunately, digital systems expressible as automata have left-total transition relations (there is always at least one next state).

3. We know that  $\hat{K} \not\models \phi$ , but the counterexample for  $\hat{K}$  is not a counterexample for K (it is *spurious*). Refine  $\hat{K}$  somehow, so the abstract paths ideally cover fewer concrete paths, and go back to Step 1.

The core CEGAR methodology can be implemented in various ways, not dictating the choice of the abstract state space beyond existential abstraction nor the choices of refinement. However, it cannot verify properties such as the recovery properties discussed in Example 2.2.2, because they contain both universal and existential quantifiers in negation normal form.

Three-Valued Abstraction Refinement (TVAR). The TVAR methodology allows verification of full propositional  $\mu$ -calculus and its fragments such as CTL\*, CTL, and LTL. For  $\hat{K}$ , extensions of Kripke structures are used. A Partial Kripke Structure (PKS) introduces the possibility of state labellings being unknown, which means there is a possibility of an unknown result of model-checking  $\hat{K}$ , in which case  $\hat{K}$  is refined. A Kripke Modal Transition System (KMTS) structure further introduces the possibility of transitions having an unknown presence.

Unfortunately, as TVAR is not limited to specification with path counterexamples, the algorithms for verification tend to be more complicated, and it is not as easy to provide a counterexample when a property is violated. The TVAR frameworks and structures will be explored in detail in Chapter 4.

#### 2.5.2 Abstraction Domains

To properly and effectively leverage abstraction, we need to decide how the system will be abstracted, keeping the number of reachable abstract states low but with enough information needed to verify the properties. In practice, it is also necessary to be able to compute the transition function for the abstract states reasonably fast.

Digital system states are typically composed of separate variables. We can assign abstract domains to the variables to form the abstraction. There are two general groups of abstract domains, non-relational and relational. We are mostly interested in bit-vector domains since bit-vectors are commonly used in digital systems, as previously discussed in Subsection 2.1.2.

The abstract domains can be considered using various underlying formalisms. For model checking with abstraction refinement, existential abstraction is sufficient, but it is common to describe domains using abstract interpretation, which extends existential abstraction and allows using additional algorithms.

In non-relational domains, each variable is considered separately. Some examples of domains for bit-vectors are:

- Constant domain. The abstract bit-vector either has a constant value or can have any value  $(\top)$ .

- **Sign domain.** Only the signedness of the bit-vector in the two's complement is retained. Zero can be treated as a special value as well, and any possibility (negative,

zero, positive) is represented by  $\top$ , resulting in the abstract value being represented by  $\{-,0,+,\top\}$ . Other variations are also possible, e.g. also considering non-negative and non-positive abstract values.

- Interval domain. The abstract bit-vector value is restricted to some interval. This requires interpreting the bit-vector value as a number, differing depending on whether we consider it to be signed or unsigned. Problematically, signedness may vary depending on the machine-code instruction or hardware operation, leading to research into wrap-around arithmetic [24].

- Three-valued bit-vector domain. Each bit of the bit-vector is considered as separate, expressed in three-valued logic. This domain is discussed in detail in Chapter 5.

Relational domains allow expressing relationships between variables, such as the octagon abstract domain [25]. The richest abstraction domain is predicate abstraction, where the abstract states retain information about whether some chosen predicate calculus formulas hold in them.

Note 2.5.2. The common formalism for abstract model-checking is that of lack of information, using the symbol  $\bot$  for no information. However, the common formalism for abstraction domains, coming from program verification and abstract interpretation, is that of possibilities, using the symbol  $\top$  for all possibilities. These formalisms are dual and both correspond to the third value in three-valued logic.

The choice of a suitable domain is heavily dependent on the system and the verified property<sup>5</sup>. While a more descriptive abstraction may reduce state space explosion, its effectiveness may be limited due to slower computation of transitions.

It has been previously observed that a major exponential explosion in formal verification of machine-code programs occurs when reading the General Purpose Input/Output (GPIO) port values [26, 27, 28], an instance of this phenomenon already discussed in Example 2.3.3. The most suitable domain for resolving this problem is the three-valued bit-vector domain, which I decided to use in my diploma thesis [A.4]. However, it was previously not possible to perform arithmetic operations in the three-valued bit-vector domain without exponential explosion within the operation, leading me to devise new algorithms that solve this problem, as described in Chapter 5.

Note 2.5.3. I conducted some preliminary research into interval abstraction for machine-code verification, but it is not integrated into my tool **machine-check** yet. While I think that it is worthwhile to use other abstraction domains in addition to the three-valued bit-vector domain, they are outside of the scope of this thesis.

$<sup>^{5}</sup>$ If we had an oracle that could always choose the domain resulting in the quickest verification with a non- $\bot$  result, verification would be quick and there would be no need for abstraction refinement.

## 2.6 State of the Art in Digital System Verification

By comparing the state-of-the-art formal verification tools for hardware, source-code, and machine-code systems, we can discover how the differences in the system levels result in differences in approaches taken to describe and verify the systems. I will discuss source-code and hardware verification first as they are used in practice with a variety of competing tools [29]. I will restrict the discussion to freely available verification tools and scientific research. Even though the basic techniques used in commercial tools may be similar to the ones in freely available tools, the details are not well-known.

#### 2.6.1 Source-Code Systems

The main source for determining the state of the art in formal verification of source-code systems is the **SV-COMP** competition, organised yearly from 2012 onwards. In the latest competition [30], there were 59 verification tools participating, showing that source-code verification is highly established in the formal verification community. The main programming language in SV-COMP and most competing tools is the C language, widely used e.g. in operating system kernels and drivers where programming bugs can severely impact the security or safety of the affected computers. In the latest **SV-COMP** competition, there were 30300 C verification tasks [30, p. 300], showing the maturity of work on benchmarking of source-code verification. Nevertheless, good results in **SV-COMP** do not necessarily mean that the tools are applicable to industrial use [31].

Notably, all specifications in **SV-COMP** are simple LTL formulas in the form  $\mathbf{G}\phi$ , where  $\phi$  is an atomic property, or  $\mathbf{F}\phi$  for termination [32]. As such, it is possible to verify the specifications using simpler reachability-based algorithms rather than the algorithms for checking e.g. LTL, CTL, or CTL\* specifications. Simple path-based counterexamples can be generated where  $\mathbf{G}\phi$  is violated. I would argue that the focus on degenerate specifications may be detrimental to the diversity of research: there is no quantitative motivation for verifying more complex specifications that correspond to less trivial violations. Instead, the verification tools are incentivised to present quantitative improvement for the degenerate specifications.

While there are many participating tools in **SV-COMP**, two tools stand out in particular, frequently placing in top three or winning many categories: **CPAchecker**<sup>6</sup> [33] and **Ultimate Automizer**, part of the **Ultimate** program analysis framework [34]. Notably, both of the tools use CEGAR and encode the program and the property into Satisfiability Modulo Theories (SMT) formulas which are checked by underlying SMT solver tools [30, 35]. Further techniques are used to extend this basic concept or introduce additional improvements, but they are beyond the scope of this thesis.